# Microsoft Window 915

# OZ6860 Mercury CardBus Controller

# Features

- Single-chip CardBus host adapter

- Supports 2 PCMCIA 2.1 & JEIDA 4.2 R2 cards or 2 CardBus cards

- Supports multiple FIFOs for PCI/CB data transfer

- Supports up to 33 MHz clock to CardBus cards

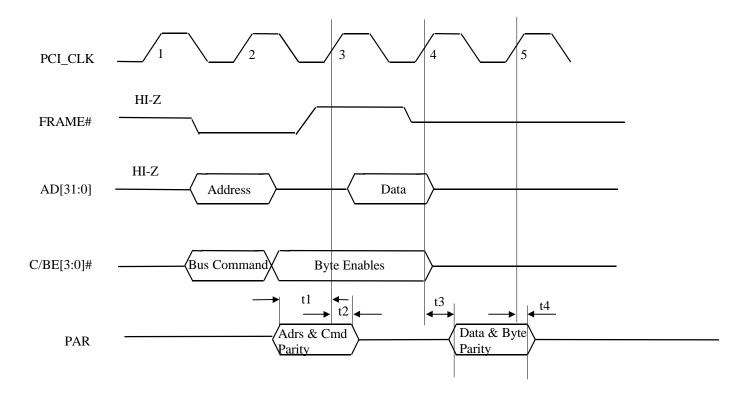

- Compliant with PCI spec. V2.1S , 1995 PC Card Standard & JEIDA 4.1

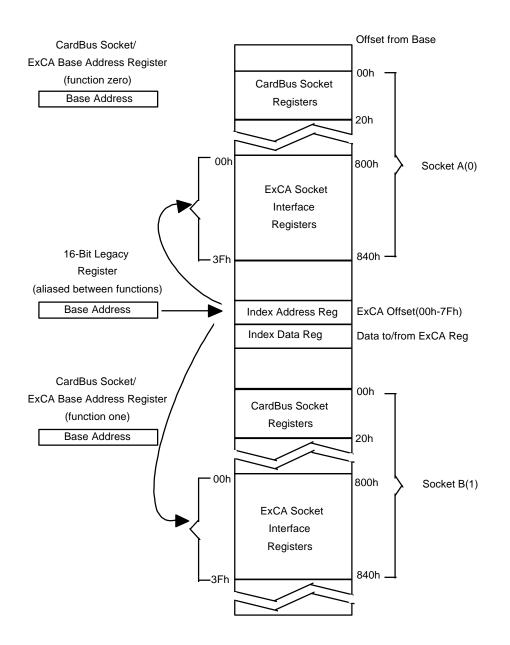

- OZ672X-compatible register set, ExCA<sup>™</sup>- compatible

- Yenta<sup>™</sup> -PCI to PCMCIA CardBus Bridge register compatible

- ACPI-PCI Bus Power management Interface Specification Rev1.0 compliant

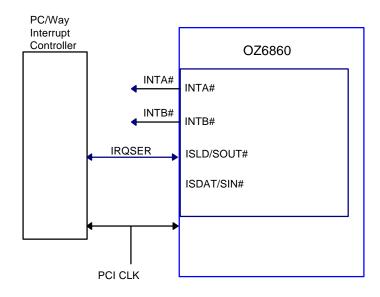

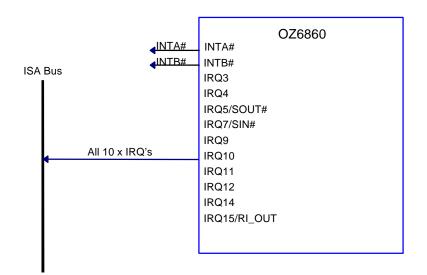

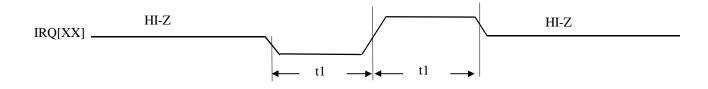

- Programmable interrupt protocol : PCI + Parallel ISA Legacy IRQ, PCI, PCI/Way, or PC/PCI Interrupt Signaling modes

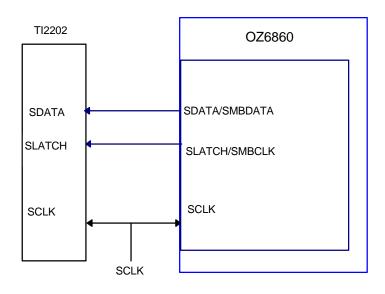

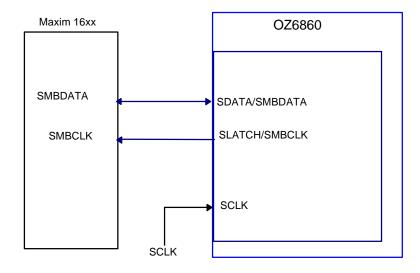

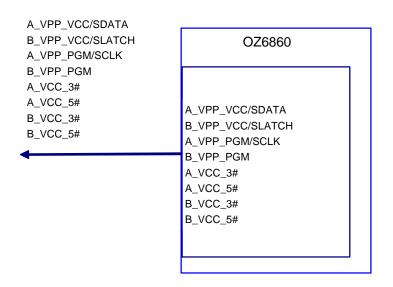

- Parallel or Serial interface to socket power control devices

3V card protection during host system suspend with Auto

- 3V card protection during nost system suspend with Auto Card VS# re-sensing

- Socket-to-socket transfer (bus master) capability

- Supports both 5V and 3.3V PC cards

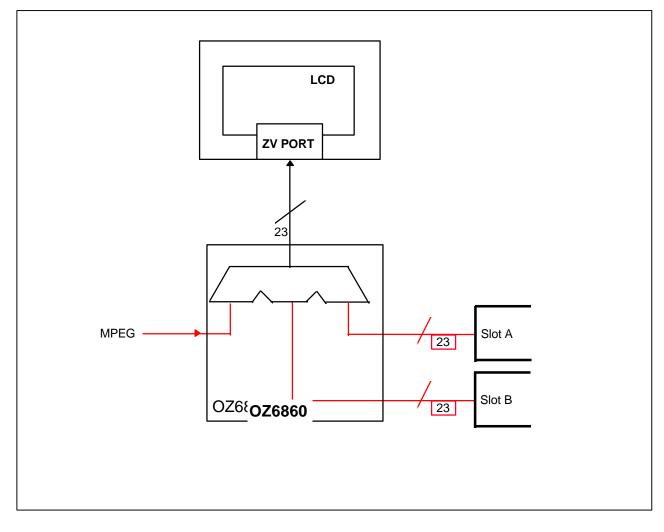

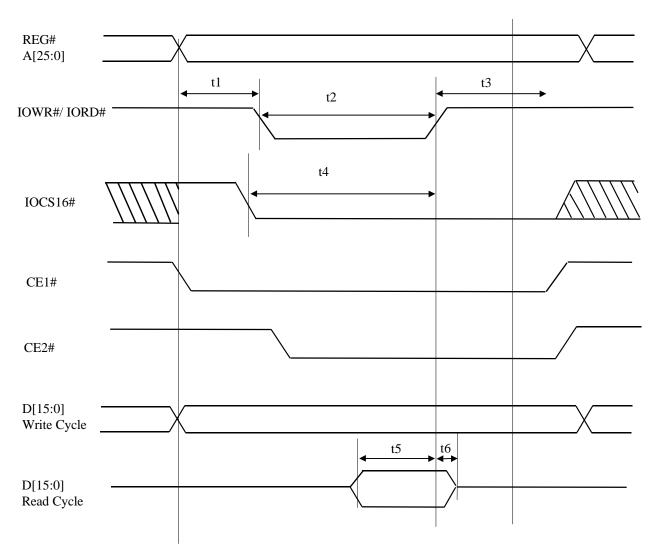

- Support PCMCIA\_ATA Specification Dual-Slot plus "Builtin" Live Video High Throughput Multimedia ZV ports support without additional buffer

- Dedicated ZV output port to LCD controller

- No buffers required for PC Card socket interface

- PC 98 -Subsystem Vendor ID support

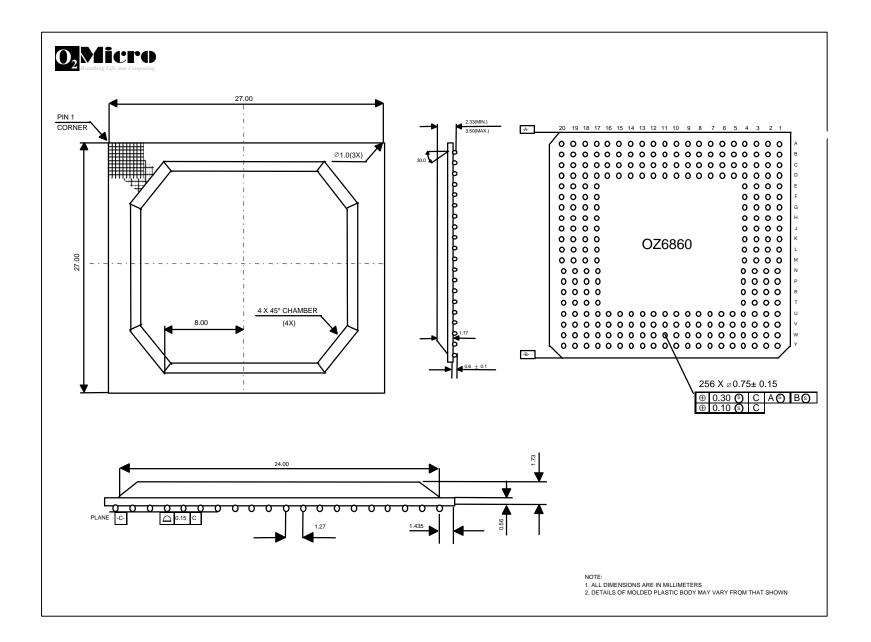

- 256 pin BGA/TQFP

# **Ordering Information**

OZ6860B - 256 pin BGA OZ6860T- 256 pin TQFP

# Description

The OZ6860 Mercury ACPI CardBus Controller provides a high performance, synchronous, 32-bit, bus master/target interface between computers and plug in PC Cards. CardBus is the new 32bit interface standard of Personal Computer Memory Card International Association, PCMCIA. The CardBus provides 32-bit interface with multiplexed address and data lines. This will allow the addition of high performance computer system enhancements and new functions in a user-friendly way. Further, the expansion capability of the CardBus will provide benefits to the end user. CardBus is intended to support "temporal" add-in functions on PC Cards, such as Memory cards, Network interfaces, FAX/Modems and other wireless communication cards, etc. The high performance and capability of the CardBus interface will enable the development of many new functions and applications.

The OZ6860 CardBus controller is a 33 MHz PCI compliant master/target device which attaches to the PCI bus and manages two PC Card sockets. The PC Card sockets will support both 3.3V/5V of either 8/16-bit PCMCIA R2 card or 32-bit CardBus card. The support for the R2 card is compatible to the Intel 82365SL PCIC controller, and the support for the CardBus card is fully compatible to the 1995 PC Card Standard CardBus specification. The OZ6860 is a stand-alone device, which means

that it does not require an additional buffer chip for the two PC Card socket interface. The OZ6860 implemented FIFO data buffer for the PCI and CardBus interface to provide better PCI bus access.

The OZ6860 supports MPEG 16bit YUV signals and 2 zoomed video sockets directly and has a dedicated output to the Zoomed Video port of the LCD panel without the need for costly external buffers. The FIFO buffers allow the bridge to accept data from a target bus while trying to move data to it. This will help prevent deadlocks. In addition, the OZ6860 is equipped with dynamic PC Card Hot Insertion and Removal and auto configuration capabilities.

The OZ6860 provides mixed 5v/3.3v capability for power saving. An advanced CMOS process is utilized to minimize system power consumption. The device also provides a power-down mode to allow host software to reduce power consumption further while stopping internal clock distribution and the clocks on PC Card sockets. The OZ6860 is not only a CardBus bridge, but also a socket controller. The OZ6860 supports two master devices and arbitrates the priority of each. Further, the OZ6860 supports inter CardBus direct data transfer. The register set in the OZ6860 supports is the superset of the OZ67xx register set, assuring full compatibility with existing socket/card-services software and PC-card applications. The OZ6860 is a 256 pin BGA/TQFP PCMCIA R2/CardBus controller, which provides the most advanced design flexibility for the PC Cards interface in notebook computer design.

The OZ6860 is a PC Card Interface Controller, which can support both R2 cards (compliant to PCMCIA 2.1,  $ExCA^{TM}$ , and JEIDA 4.2), and CardBus cards concurrently.

To enhance the performance between the PCI bus and any CardBus card, 2 buffers (each composed of 16 double words) are added on both sides going from PCI to CB, or CB to PCI. By implementing these buffers, OZ6860 will not refuse the data from a target bus while trying to move data to it and prevent deadlock situations.

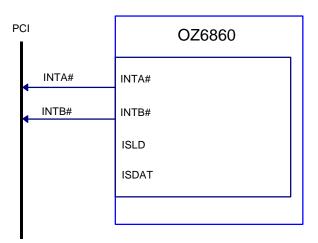

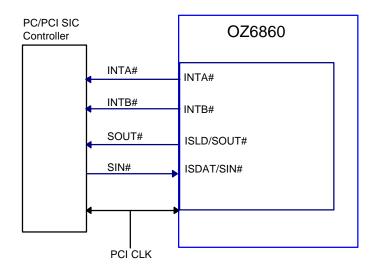

In order to allow maximum flexibility for system designers, the CINT# of the PC card 32-bit can be programmed to be steered to either INTA# or INTB# of the PCI bus. Further, the interrupts may be programmed to be routed through the bridge to either PCI INT lines or to IRQ interrupts on the ISA bus. The OZ6860 can support PCI INT lines and ISA legacy parallel IRQ or Serial IRQ mode at the same time. CardBus cards use the PCI INT, and PC 16 bit cards use ISA legacy IRQ. The OZ6860 supports the PSI + ISA Legacy parallel IRQ mode to save system cost by not adding the serial to parallel external hardware.

The OZ6860 supports ACPI (Advanced Configuration and Power Interface) specification v1.0, which is the key element in Operating System Directed Power Management (OSPM). To facilitate ACPI, the OZ6860 has built-in registers to allow the implementation of new PCI Power Management Capabilities and the support for different power states.

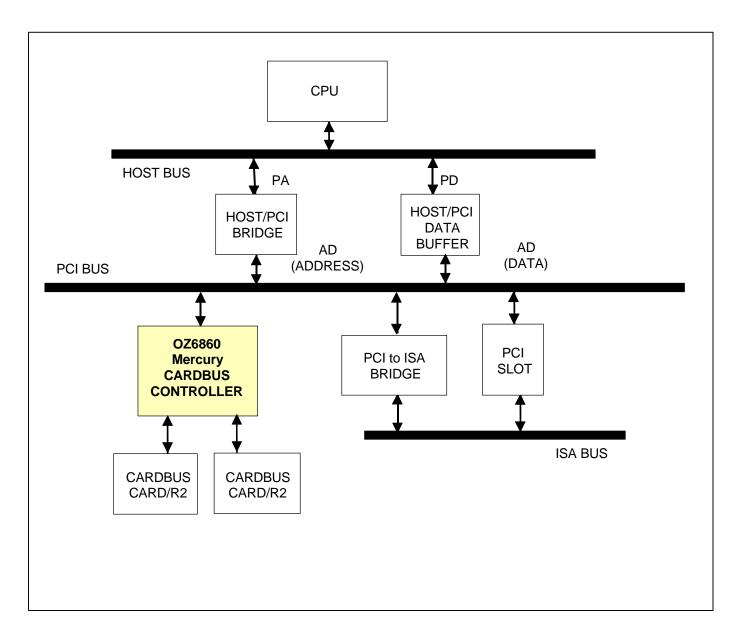

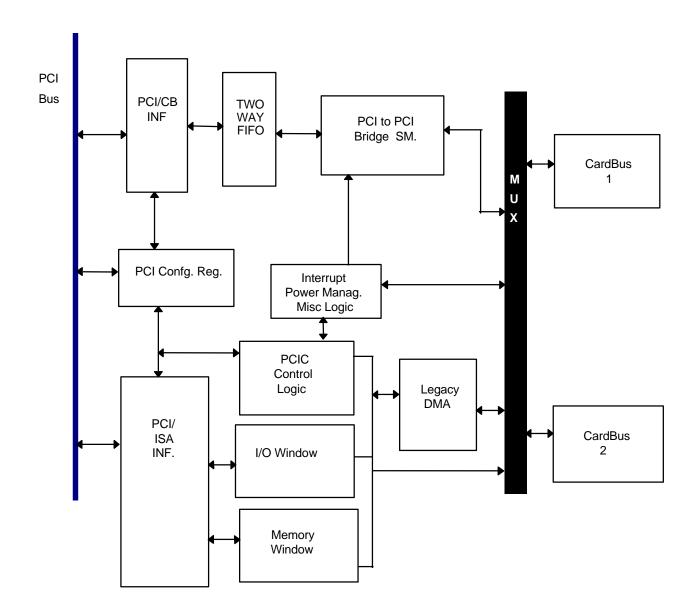

# System Block Diagram

The following diagram is a typical system block diagram utilizing the OZ6860 "*Mercury*" CardBus controller with other related chipset.

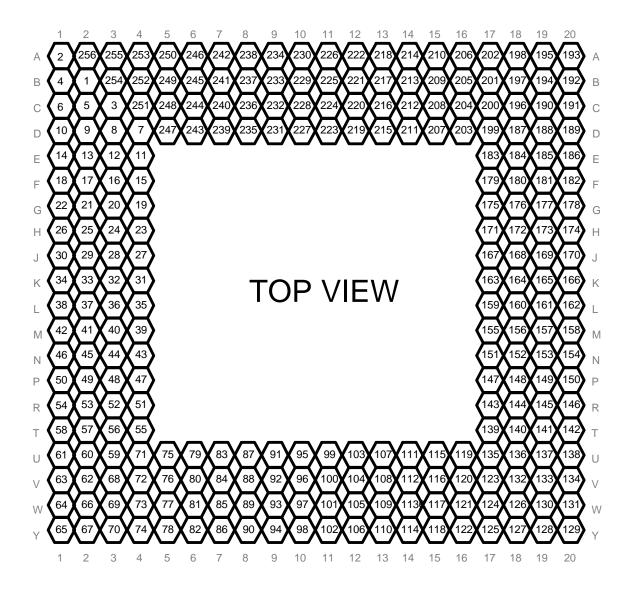

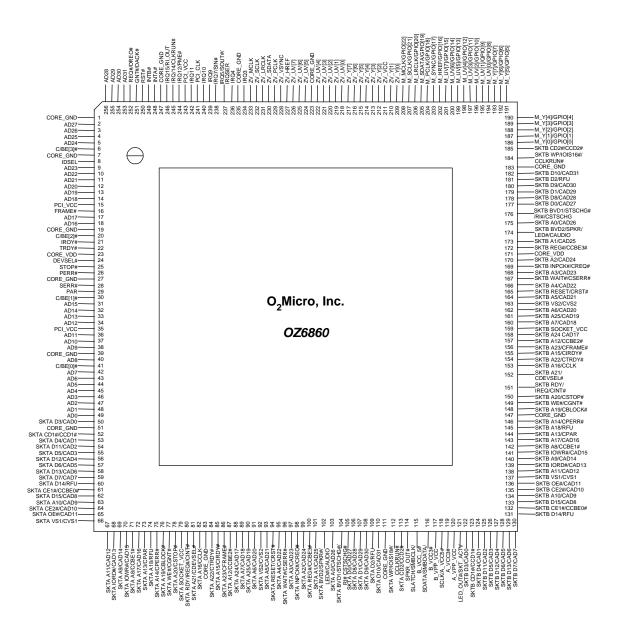

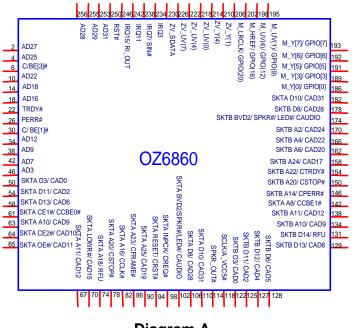

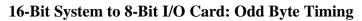

# Pin Diagram

The following diagram shows the top view of the 256 pin BGA package

The following four diagrams show the complete pin-out (with pin name) of the OZ6860. For simplicity, the pin-out has been split into four diagrams. Diagram A will correspond to the pins on the outermost edge of the part. Diagram D will correspond to the inner most pins of the part.

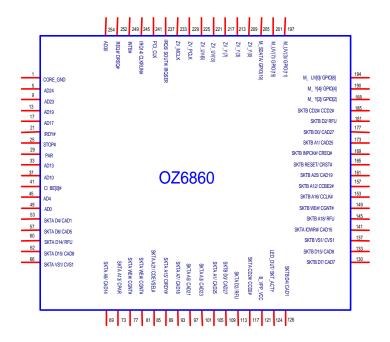

**Diagram A**

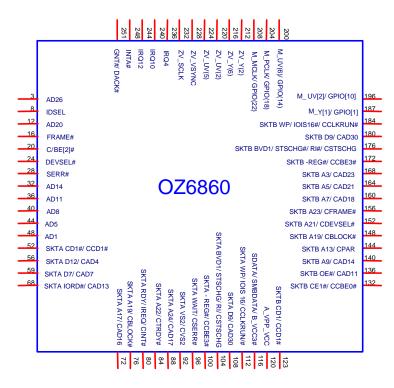

### **Diagram B**

**Diagram C**

# **Diagram D**

# Pin List

| 1       CORE_GND         2       AD[27]         3       AD[26]         4       AD[25]         5       AD[24]         6       C/ BE[3]#         7       CORE_GND         8       IDSEL         9       AD[22]         11       AD[21]         12       AD[20]         13       AD[19]         14       AD[17]         18       AD[16]         19       CORE_GND         20       C/BE[2]#         21       IRDY#         22       TRDY#         23       CORE_VDD         24       DEVSEL#         25       STOP#         26       PER##         27       CORE_GND         28       SERR#         29       PAR         30       C/BE[1]#         31       AD[15]         32       AD[14]         33       AD[13]         34       AD[12]         35       PCL_VCC         36       AD[11]         37       AD[10]         38       AD[9]         39                                                                                                                                            | Pin Number | Pin Name              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|

| 3       AD[26]         4       AD[25]         5       AD[24]         6       C/ BE[3]#         7       CORE_GND         8       IDSEL         9       AD[23]         10       AD[22]         11       AD[21]         12       AD[20]         13       AD[19]         14       AD[17]         18       AD[16]         19       CORE_GND         20       C /BE[2]#         21       IRDY#         22       TRDY#         23       CORE_VDD         24       DEVSEL#         25       STOP#         26       PERR#         29       PAR         30       C/BE[1]#         31       AD[15]         32       AD[14]         33       AD[13]         34       AD[12]         35       PCL_VCC         36       AD[11]         37       AD[10]         38       AD[9]         39       CORE_GND         41       C/BE[0]#         42       AD[7]         43 <th>1</th> <th></th>                                                                                                                    | 1          |                       |

| 4       AD[25]         5       AD[24]         6       C/ BE[3]#         7       CORE_GND         8       IDSEL         9       AD[23]         10       AD[22]         11       AD[21]         12       AD[20]         13       AD[19]         14       AD[18]         15       PCL_VCC         16       FRAME#         17       AD[17]         18       AD[16]         19       CORE_GND         20       C/BE[2]#         21       IRDY#         22       TRDY#         23       CORE_VDD         24       DEVSEL#         25       STOP#         26       PERR#         27       CORE_GND         28       SER#         29       PAR         30       C/ BE[1]#         31       AD[15]         32       AD[14]         33       AD[13]         34       AD[12]         35       PCL_VCC         36       AD[11]         37       AD[10]         38 <th>2</th> <th>AD[27]</th>                                                                                                              | 2          | AD[27]                |

| 5       AD[24]         6 $C/BE[3]^{\#}$ 7       CORE_GND         8       IDSEL         9       AD[23]         10       AD[22]         11       AD[20]         13       AD[19]         14       AD[18]         15       PCI_VCC         16       FRAME#         17       AD[16]         19       CORE_GND         20       C /BE[2]#         21       IRDY#         22       TRDY#         23       CORE_VDD         24       DEVSEL#         25       STOP#         26       PERR#         27       CORE_GND         28       SERR#         29       PAR         30       C/BE[1]#         31       AD[15]         32       AD[14]         33       AD[13]         34       AD[12]         35       PCL_VCC         36       AD[11]         37       AD[10]         38       AD[9]         39       CORE_GND         40       AD[8] <td< th=""><th>3</th><th>AD[26]</th></td<>                                                                                                                | 3          | AD[26]                |

| 5       AD[24]         6 $C/BE[3]^{\#}$ 7       CORE_GND         8       IDSEL         9       AD[23]         10       AD[22]         11       AD[20]         13       AD[19]         14       AD[18]         15       PCI_VCC         16       FRAME#         17       AD[16]         19       CORE_GND         20       C /BE[2]#         21       IRDY#         22       TRDY#         23       CORE_VDD         24       DEVSEL#         25       STOP#         26       PERR#         27       CORE_GND         28       SERR#         29       PAR         30       C/BE[1]#         31       AD[15]         32       AD[14]         33       AD[13]         34       AD[12]         35       PCL_VCC         36       AD[11]         37       AD[10]         38       AD[9]         39       CORE_GND         40       AD[8] <td< th=""><th>4</th><th>AD[25]</th></td<>                                                                                                                | 4          | AD[25]                |

| 6         C/ BE[3]#           7         CORE_GND           8         IDSEL           9         AD[23]           10         AD[22]           11         AD[20]           13         AD[19]           14         AD[19]           14         AD[17]           15         PCI_VCC           16         FRAME#           17         AD[17]           18         AD[16]           19         CORE_GND           20         C /BE[2]#           21         IRDY#           22         TRDY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[13]           34         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10] <td< th=""><th>5</th><th></th></td<>                             | 5          |                       |

| 7         CORE_GND           8         IDSEL           9         AD[23]           10         AD[22]           11         AD[20]           13         AD[19]           14         AD[18]           15         PCI_VCC           16         FRAME#           17         AD[16]           19         CORE_GND           20         C/BE[2]#           21         IRDY#           22         TRDY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/BE[1]#           31         AD[15]           32         AD[14]           33         AD[13]           34         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[6]           44<                                                        |            |                       |

| 8         IDSEL           9         AD[23]           10         AD[22]           11         AD[20]           13         AD[19]           14         AD[18]           15         PCI_VCC           16         FRAME#           17         AD[17]           18         AD[16]           19         CORE_GND           20         C /BE[2]#           21         IRDY#           22         TRDY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C / BE[1]#           31         AD[15]           32         AD[14]           33         AD[13]           34         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41                                                       |            |                       |

| 9         AD[23]           10         AD[22]           11         AD[21]           12         AD[20]           13         AD[19]           14         AD[17]           15         PCI_VCC           16         FRAME#           17         AD[16]           19         CORE_GND           20         C /BE[2]#           21         IRDY#           22         TRDY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7] <td< th=""><th></th><th></th></td<>                             |            |                       |

| 10         AD[22]           11         AD[21]           12         AD[20]           13         AD[19]           14         AD[18]           15         PCI_VCC           16         FRAME#           17         AD[17]           18         AD[16]           19         CORE_GND           20         C /BE[2]#           21         IRDY#           22         TRDY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/BE[1]#           31         AD[15]           32         AD[14]           33         AD[13]           34         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           41         C/BE[0]#           42         AD[7] <t< th=""><th></th><th></th></t<>                               |            |                       |

| 11         AD[21]           12         AD[20]           13         AD[19]           14         AD[18]           15         PCI_VCC           16         FRAME#           17         AD[17]           18         AD[16]           19         CORE_GND           20         C /BE[2]#           21         IRDY#           22         TRDY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[13]           34         AD[12]           35         PCL_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           <                                                    |            |                       |

| 12         AD[20]           13         AD[19]           14         AD[18]           15         PCI_VCC           16         FRAME#           17         AD[17]           18         AD[16]           19         CORE_GND           20         C /BE[2]#           21         IRDY#           22         TRY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/BE[1]#           31         AD[15]           32         AD[14]           33         AD[13]           34         AD[12]           35         PCI_VCC           36         AD[9]           39         CORE_GND           40         AD[8]           41         C/BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46 </th <th>-</th> <th>• •</th>                            | -          | • •                   |

| 13       AD[19]         14       AD[18]         15       PCI_VCC         16       FRAME#         17       AD[17]         18       AD[16]         19       CORE_GND         20       C /BE[2]#         21       IRDY#         22       TRDY#         23       CORE_VDD         24       DEVSEL#         25       STOP#         26       PERR#         27       CORE_GND         28       SERR#         29       PAR         30       C/ BE[1]#         31       AD[12]         32       AD[14]         33       AD[12]         35       PCI_VCC         36       AD[11]         37       AD[10]         38       AD[9]         39       CORE_GND         40       AD[8]         41       C/ BE[0]#         42       AD[1]         43       AD[6]         44       AD[5]         45       AD[4]         46       AD[3]         47       AD[2]         48 </th <th></th> <th></th>                                                                                                               |            |                       |

| 14         AD[18]           15         PCI_VCC           16         FRAME#           17         AD[17]           18         AD[16]           19         CORE_GND           20         C /BE[2]#           21         IRDY#           22         TRDY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[13]           34         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           4                                                       |            |                       |

| 15 $PCI_VCC$ 16         FRAME#           17 $AD[17]$ 18 $AD[16]$ 19 $CORE_GND$ 20 $C/BE[2]#$ 21 $IRDY#$ 22 $TRDY#$ 23 $CORE_VDD$ 24 $DEVSEL#$ 25 $STOP#$ 26 $PERR#$ 27 $CORE_GND$ 28 $SERR#$ 29 $PAR$ 30 $C/BE[1]#$ 31 $AD[15]$ 32 $AD[14]$ 33 $AD[13]$ 34 $AD[12]$ 35 $PCI_VCC$ 36 $AD[11]$ 37 $AD[10]$ 38 $AD[9]$ 39 $CORE_GND$ 40 $AD[8]$ 41 $C/BE[0]#$ 42 $AD[7]$ 43 $AD[6]$ 44 $AD[3]$ 47 $AD[2]$ 48 <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                       |

| 16         FRAME#           17         AD[17]           18         AD[16]           19         CORE_GND           20         C /BE[2]#           21         IRDY#           22         TRDY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/BE[1]#           31         AD[15]           32         AD[14]           33         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49 <th></th> <th></th>                                       |            |                       |

| 17         AD[17]           18         AD[16]           19         CORE_GND           20         C /BE[2]#           21         IRDY#           22         TRDY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[13]           34         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49 <th></th> <th></th>                                      |            |                       |

| 18         AD[16]           19         CORE_GND           20         C /BE[2]#           21         IRDY#           22         TRDY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/BE[1]#           31         AD[15]           32         AD[14]           33         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/CAD[0]           <                                                   |            |                       |

| 19         CORE_GND           20         C /BE[2]#           21         IRDY#           22         TRDY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/BE[1]#           31         AD[15]           32         AD[14]           33         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/CAD[0]           51         CORE_GND                                                            |            |                       |

| 20         C /BE[2]#           21         IRDY#           22         TRDY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/BE[1]#           31         AD[15]           32         AD[14]           33         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/CCD[1]#                                                |            |                       |

| 21         IRDY#           22         TRDY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/CCD[1]#           53         SKTA: D[4]/CAD[2]                                       | -          |                       |

| 22         TRDY#           23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/CCD[1]#           53         SKTA: D[4]/CAD[1]           54         SKTA: D[4]/CAD[                             |            |                       |

| 23         CORE_VDD           24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55 <td< th=""><th></th><th></th></td<> |            |                       |

| 24         DEVSEL#           25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56                           |            |                       |

| 25         STOP#           26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                            |            |                       |

| 26         PERR#           27         CORE_GND           28         SERR#           29         PAR           30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[12]           35         PCL_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: D[1]// CAD[1]           54         SKTA: D[1]/ CAD[1]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                 |            |                       |

| 27         CORE_GND           28         SERR#           29         PAR           30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[12]           35         PCL_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: D[1]// CAD[1]           54         SKTA: D[1]/ CAD[1]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                       |            |                       |

| 28         SERR#           29         PAR           30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/CCD[1]#           53         SKTA: D[4]/CAD[1]           54         SKTA: D[5]/CAD[3]           56         SKTA: D[12]/CAD[4]                                                                                                                                                             |            |                       |

| 29         PAR           30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[13]           34         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                  |            |                       |

| 30         C/ BE[1]#           31         AD[15]           32         AD[14]           33         AD[13]           34         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                |            |                       |

| 31         AD[15]           32         AD[14]           33         AD[13]           34         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[5]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                       |            |                       |

| 32         AD[14]           33         AD[13]           34         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: D[1]// CAD[1]           53         SKTA: D[1]/ CAD[1]           54         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                             |            |                       |

| 33         AD[13]           34         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                       |            | • •                   |

| 34         AD[12]           35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                   |            | • •                   |

| 35         PCI_VCC           36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                       |            |                       |

| 36         AD[11]           37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                            |            |                       |

| 37         AD[10]           38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                |            |                       |

| 38         AD[9]           39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                            |            |                       |

| 39         CORE_GND           40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                       |            |                       |

| 40         AD[8]           41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                       |

| 41         C/ BE[0]#           42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39         |                       |

| 42         AD[7]           43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4] <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |                       |

| 43         AD[6]           44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |                       |

| 44         AD[5]           45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |                       |

| 45         AD[4]           46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                       |

| 46         AD[3]           47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | • •                   |

| 47         AD[2]           48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45         |                       |

| 48         AD[1]           49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46         | AD[3]                 |

| 49         AD[0]           50         SKTA: D[3]/ CAD[0]           51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[1]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47         | AD[2]                 |

| 50         SKTA:         D[3]/ CAD[0]           51         CORE_GND           52         SKTA:         CD[1]#/ CCD[1]#           53         SKTA:         D[4]/ CAD[1]           54         SKTA:         D[11]/ CAD[2]           55         SKTA:         D[5]/ CAD[3]           56         SKTA:         D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 48         | AD[1]                 |

| 51         CORE_GND           52         SKTA: CD[1]#/ CCD[1]#           53         SKTA: D[4]/ CAD[1]           54         SKTA: D[11]/ CAD[2]           55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49         | AD[0]                 |

| 52         SKTA:         CD[1]#/         CCD[1]#           53         SKTA:         D[4]/         CAD[1]           54         SKTA:         D[11]/         CAD[2]           55         SKTA:         D[5]/         CAD[3]           56         SKTA:         D[12]/         CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50         |                       |

| 53         SKTA:         D[4]/ CAD[1]           54         SKTA:         D[11]/ CAD[2]           55         SKTA:         D[5]/ CAD[3]           56         SKTA:         D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51         |                       |

| 53         SKTA:         D[4]/ CAD[1]           54         SKTA:         D[11]/ CAD[2]           55         SKTA:         D[5]/ CAD[3]           56         SKTA:         D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52         | SKTA: CD[1]#/ CCD[1]# |

| 54         SKTA:         D[11]/         CAD[2]           55         SKTA:         D[5]/         CAD[3]           56         SKTA:         D[12]/         CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53         |                       |

| 55         SKTA: D[5]/ CAD[3]           56         SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54         |                       |

| 56 SKTA: D[12]/ CAD[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55         |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 56         |                       |

| 57 SKTA: D[6]/ CAD[5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57         | SKTA: D[6]/ CAD[5]    |

| 58 SKTA: D[13]/ CAD[6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58         |                       |

| Pin Number      | Pin Name                                                           |

|-----------------|--------------------------------------------------------------------|

| 59              | SKTA: D[7]/ CAD[7]                                                 |

| 60              | SKTA: D[14]/ RFU                                                   |

| 61              | SKTA: CE[1]#/ CCBE[0]#                                             |

| 62              | SKTA: D[15]/ CAD[8]                                                |

| 63              | SKTA: A[10]/ CAD[9]                                                |

| 64              |                                                                    |

|                 | SKTA: CE[2]#/ CAD[10]                                              |

| <u>65</u><br>66 | SKTA:         OE#/ CAD[11]           SKTA:         VS1/ CVS1       |

| 67              | SKTA: VS1/CVS1<br>SKTA: A[11]/CAD[12]                              |

|                 |                                                                    |

| 68              | SKTA:         IORD#/ CAD[13]           SKTA:         A[9]/ CAD[14] |

| 69              |                                                                    |

| 70              | SKTA: IOWR#/ CAD[15]                                               |

|                 | SKTA: A[8]/ CCBE[1]#                                               |

| 72<br>73        | SKTA: A[17]/ CAD[16]                                               |

| 73              | SKTA: A[13]/ CPAR                                                  |

|                 | SKTA: A[18]/ RFU                                                   |

| 75              | SKTA: A[14]/ CPERR#                                                |

| 76              | SKTA: A[19]/ CBLOCK#                                               |

| 77              | SKTA: WE#/ CGNT#                                                   |

| 78              | SKTA: A[20]/ CSTOP#                                                |

| 79              | SKTA: SOCKET_VCC                                                   |

| 80              | SKTA: RDY/ IREQ#/ CINT#                                            |

| 81              | SKTA: A[21]/ CDEVSEL#                                              |

| 82              | SKTA: A[16]/ CCLK#                                                 |

| 83              | CORE_GND                                                           |

| 84              | SKTA: A[22]/ CTRDY#                                                |

| 85              | SKTA: A[15]/ CIRDY#                                                |

| 86              | SKTA: A[23]/ CFRAME#                                               |

| 87              | SKTA: A[12]/ CCBE[2]#                                              |

| 88              | SKTA: A[24]/ CAD[17]                                               |

| 89              | SKTA: A[7]/CAD[18]                                                 |

| 90<br>91        | SKTA: A[25]/ CAD[19]<br>SKTA: A[6]/ CAD[20]                        |

| 91              | SKTA: A[0]/ CAD[20]<br>SKTA: VS2/ CVS2                             |

| 92              | SKTA: V32/CV32<br>SKTA: A[5]/CAD[21]                               |

| 94              | SKTA: A[5]/ CAD[21]<br>SKTA: RESET/ CRST#                          |

| 94              | SKTA: RESET/CRST#<br>SKTA: A[4]/ CAD[22]                           |

| 96              | SKTA: A[4]/ CAD[22]<br>SKTA: WAIT#/ CSERR#                         |

| 97              | SKTA: WAIT#/ CSERK#<br>SKTA: A[3]/ CAD[23]                         |

| 98              | SKTA: INPCK#/ CREQ#                                                |

| 99              | SKTA: A[2]/ CAD[24]                                                |

| 100             | SKTA: REG#/ CCBE[3]#                                               |

| 100             | SKTA: A[1]/ CAD[25]                                                |

| 101             | SKTA: BVD[2]/ SPKR#/ LED#/ CAUDIO                                  |

| 102             | SKTA: A[0]/ CAD[26]                                                |

| 103             | SKTA: BVD[1]/ STSCHG#/ RI#/ CSTSCHG                                |

| 104             | SKTA: D[0]/ CAD[27]                                                |

| 105             | SKTA: D[8]/ CAD[28]                                                |

| 107             | SKTA: D[1]/ CAD[29]                                                |

| 107             | SKTA: D[1]/ CAD[29]<br>SKTA: D[9]/ CAD[30]                         |

| 109             | SKTA: D[3]/ RFU                                                    |

| 110             | SKTA: D[2]/ KTO<br>SKTA: D[10]/ CAD[31]                            |

| 111             | CORE GND                                                           |

| 112             | SKTA: WP/ IOIS16#/ CCLKRUN#                                        |

| 112             | SKTA: CD[2]#/ CCD[2]#                                              |

| 114             | SPKR_OUT#                                                          |

| 115             | SLATCH/ SMBCLK/ B_VCC5#                                            |

| 116             | SDATA/ SMBDTA/ B_VCC3#                                             |

| 110             | 00,1,1,4 01100 174 0_4000#                                         |

# OZ6860

| Pin Number        | Pin Name                                    | Pin Number        | Pin Name                               |

|-------------------|---------------------------------------------|-------------------|----------------------------------------|

| 117               | B_VPP_VCC                                   | 179               | SKTB: D[1]/ CAD[29]                    |

| 118               | SCLK/ A_VCC5#                               | 180               | SKTB: D[9]/ CAD[30]                    |

| 119               | A_VCC3#                                     | 181               | SKTB: D[2]/ RFU                        |

| 120               |                                             | 182               | SKTB: D[10]/ CAD[31]                   |

| 121               | LED_OUT#/ SKT_ACTV                          | 183               | CORE_GND                               |

| 122               | SKTB: D[3]/ CAD[0]                          | 184               | SKTB: WP/ IOIS16#/ CCLKRUN#            |

| 123               | SKTB: CD[1]#/ CCD[1]#                       | 185               | SKTB: CD[2]#/ CCD[2]#                  |

| 124               | SKTB: D[4]/ CAD[1]                          | 186               | M_Y[0]/ GPIO[0]                        |

| 125               | SKTB: D[11]/ CAD[2]                         | 187               | M_Y[1]/ GPIO[1]                        |

| 126               | SKTB: D[5]/ CAD[3]                          | 188               | M_Y[2]/ GPIO[2]                        |

| 127               | SKTB: D[12]/ CAD[4]                         | 189               | M_Y[3]/ GPIO[3]                        |

| 128               | SKTB: D[6]/ CAD[5]                          | 190               | M_Y[4]/ GPIO[4]                        |

| 129               | SKTB: D[13]/ CAD[6]                         | 191               | M_Y[5]/ GPIO[5]                        |

| 130               | SKTB: D[7]/CAD[7]                           | 192               | M_Y[6]/ GPI0[6]                        |

| 131               | SKTB: D[14]/ RFU                            | 193               | M_Y[7]/ GPI0[7]                        |

| 132               | SKTB: CE[1]#/ CCBE[0]#                      | 194               | M_UV[0]/ GPIO[8]                       |

| 133               | SKTB: D[15]/ CAD[8]                         | 195               | M_UV[1]/ GPI0[9]                       |

| 134               | SKTB: A[10]/ CAD[9]                         | <u>196</u><br>197 | M_UV[2]/ GPIO[10]<br>M_UV[3]/ GPIO[11] |

| <u>135</u><br>136 | SKTB: CE[2]#/ CAD[10]<br>SKTB: OE#/ CAD[11] | 197               | M_UV[3]/ GPI0[11]<br>M_UV[4]/ GPI0[12] |

| 136               | SKTB: UE#/ CAD[11]<br>SKTB: VS1/ CVS1       | 198               | M_UV[5]/ GPI0[12]                      |

| 137               | SKTB: V31/CV31<br>SKTB: A[11]/ CAD[12]      | 200               | M_UV[6]/ GPI0[13]                      |

| 139               | SKTB: IORD#/ CAD[13]                        | 200               | M_UV[7]/ GPIO[15]                      |

| 140               | SKTB: 10KD#/ CAD[13]                        | 201               | M_HREF/ GPIO[16]                       |

| 141               | SKTB: IOWR#/ CAD[15]                        | 202               | M_VSYNC_BPIO[17]                       |

| 142               | SKTB: A[8]/ CCBE[1]#                        | 204               | M_PCLK/ GPIO[18]                       |

| 143               | SKTB: A[17]/ CAD[16]                        | 205               | M_SDATA/ GPIO[19]                      |

| 144               | SKTB: A[13]/ CPAR                           | 206               | M_LRCLK/ GPIO[20]                      |

| 145               | SKTB: A[18]/ RFU                            | 207               | M_SCLK/ GPIO[21]                       |

| 146               | SKTB: A[14]/ CPERR#                         | 208               | M_MCLK/ GPIO[22]                       |

| 147               | CORE_GND                                    | 209               | ZV_Y[0]                                |

| 148               | SKTB: A[19]/ CBLOCK#                        | 210               | ZV_Y[1]                                |

| 149               | SKTB: WE#/ CGNT#                            | 211               | ZV_VCC                                 |

| 150               | SKTB: A[20]/ CSTOP#                         | 212               | ZV_Y[2]                                |

| 151               | SKTB: RDY/ IREQ#/ CINT#                     | 213               | ZV_Y[3]                                |

| 152               | SKTB: A[21]/ CDEVSEL#                       | 214               | ZV_Y[4]                                |

| 153               | SKTB: A[16]/ CCLK#                          | 215               | ZV_Y[5]                                |

| 154               | SKTB: A[22]/ CTRDY#                         | 216               | ZV_Y[6]                                |

| 155               | SKTB: A[15]/ CIRDY#                         | 217               | ZV_Y[7]                                |

| 156               | SKTB: A[23]/ CFRAME#                        | 218               | ZV_UV[0]                               |

| 157               | SKTB: A[12]/ CCBE[2]#                       | 219               | ZV_UV[1]                               |

| 158               | SKTB: A[24]/ CAD[17]                        | 220               | ZV_UV[2]<br>ZV_UV[3]                   |

| <u>159</u><br>160 | SKTB: SOCKET_VCC<br>SKTB: A[7]/ CAD[18]     | 221               |                                        |

| 160               | SKTB: A[7]/ CAD[16]<br>SKTB: A[25]/ CAD[19] | <u>222</u><br>223 | ZV_UV[4]<br>CORE_GND                   |

| 162               | SKTB: A[25]/ CAD[19]<br>SKTB: A[6]/ CAD[20] | 223               | ZV_UV[5]                               |

| 163               | SKTB: VS2/CVS2                              | 225               | ZV_UV[6]                               |

| 164               | SKTB: A[5]/ CAD[21]                         | 226               | ZV_UV[7]                               |