# Challenger ACPI CardBus Controller

# FEATURES

- ACPI-PCI Bus Power Management Interface Specification Rev1.0 Compliant

- Supports OnNow LAN wakeup, OnNow Ring Indicate, PCI CLKRUN#, PME#, and CardBus CCLKRUN#

- Compliant with PCI specification v2.1S, 1998 PC Card Standard 6.1 and JEIDA 4.1

- Yenta<sup>™</sup> PCI to PCMCIA CardBus Bridge register compatible

- ExCA (Exchangeable Card Architecture) compatible registers mappable in memory and I/O space

- Intel<sup>™</sup> 82365SL PCIC Register Compatible

- Supports PCMCIA\_ATA Specification

- Supports 5V/3.3V PC Cards and 3.3V Cardbus cards

- Supports single PC Card or CardBus slot with hot insertion and removal

- Supports multiple FIFOs for PCI/CardBus data transfer

- Supports Direct Memory Access for PC/PCI and PC/Way on PC Card socket

- Programmable interrupt protocol: PCI, PCI+ISA, PCI/Way, or PC/PCI interrupt signaling modes

- Win'98 IRQ and PC-97/98 compliant

- Parallel or Serial interface for socket power control devices (Micrel or standard)

- Zoomed Video Support

- Integrated PC 98 -Subsystem Vendor ID support, with auto lock bit

- LED Activity Pins

# ORDERING INFORMATION

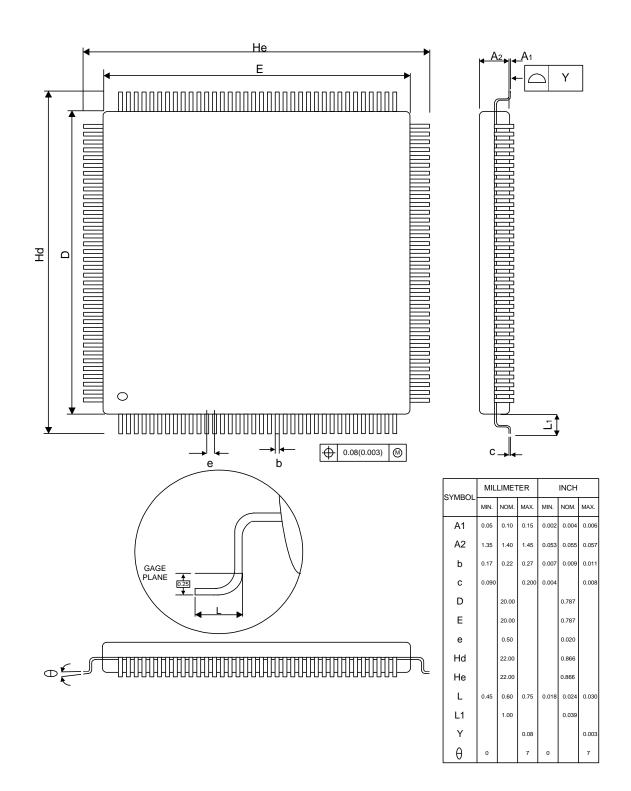

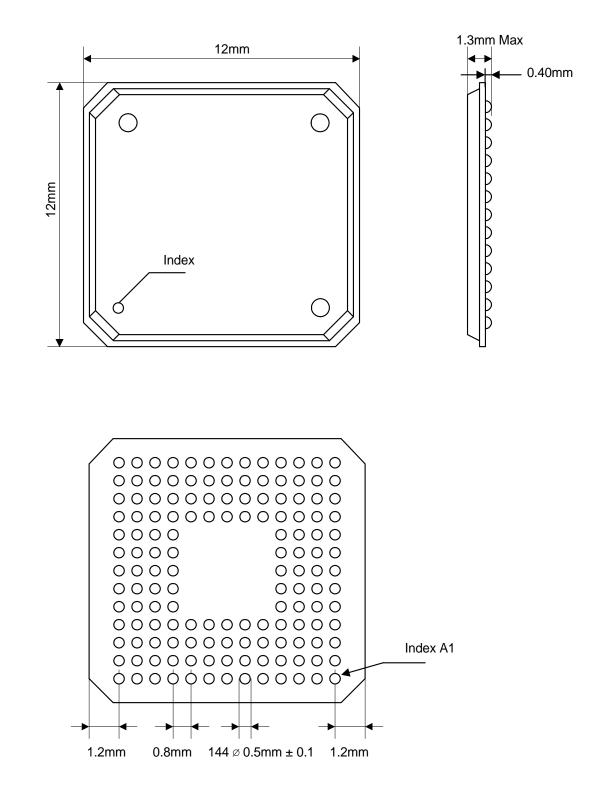

**OZ6812T** - 144pin LQFP **OZ6812B** - 144pin Mini-BGA

# **GENERAL DESCRIPTION**

The OZ6812 Challenger is an ACPI/PC98 ready, high performance, single slot PC Card controller with a synchronous 32-bit bus master/target PCI interface. This PC Card to PCI bridge host controller is compliant with the 1997 PC Card Standard. This standard incorporates the new 32-bit CardBus while retaining the 16-bit PC Card specification as defined by PCMCIA release 2.1. CardBus

is intended to support "temporal" add-in functions on PC Cards, such as Memory cards, Network interfaces, FAX/Modems and other wireless communication cards, etc. The high performance and capability of the CardBus interface will enable the new development of many new functions and applications.

Preliminary

**OZ6812**

The OZ6812 CardBus controller is compliant with the latest ACPI-PCI Bus Power Management Interface Specification. It supports all four power states and the PME# function for maximum power savings and ACPI compliance. The device also provides a power-down mode to allow host software to reduce power consumption further by stopping internal clock distribution as well as the PC Card socket clock. In addition, an advanced CMOS process is utilized to minimize system power consumption.

The OZ6812 single PCMCIA socket supports a mix and match 3.3V/5V 8/16-bit PC Card R2 card or 32-bit CardBus R3 card. The R2 card support is compatible to the Intel 82365SL PCIC controller, and the R3 card support is fully compliant with the 1997 PC Card Standard CardBus specification. The OZ6812 is a stand alone device, which means that it does not require an additional buffer chip for the PC Card socket interface. In addition, the OZ6812 supports dynamic PC Card hot insertion and removal, with auto configuration capabilities.

The OZ6812 is fully compliant with the 33Mhz PCI Bus specification, V2.1S. It supports a master device with inter CardBus direct data transfer. The OZ6812 implements a FIFO data buffer architecture between the PCI bus and CardBus socket interface to enhance data transfers to CardBus devices. The bi-directional FIFO buffer (composed of 16 double words) permits the OZ6812 to accept data from a target bus (PCI or CardBus interface) while simultaneously transferring data. This architecture not only speeds up data transfers but also prevents system deadlocks.

The OZ6812 is a PCMCIA R2/CardBus controller, providing the most advanced design flexibility for PC Cards which interface to advanced notebook designs.

# **Functional Block Diagram**

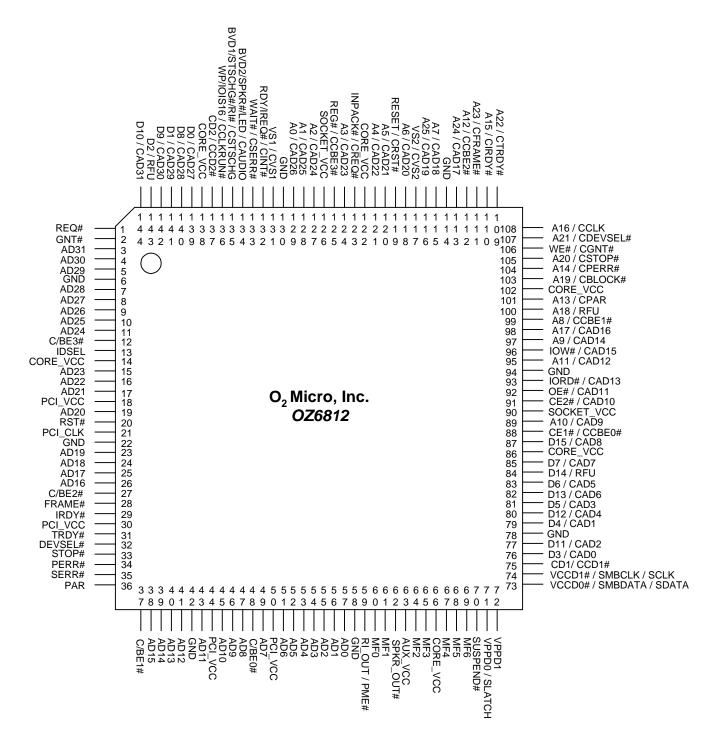

# PIN DIAGRAM - 144 Pin LQFP

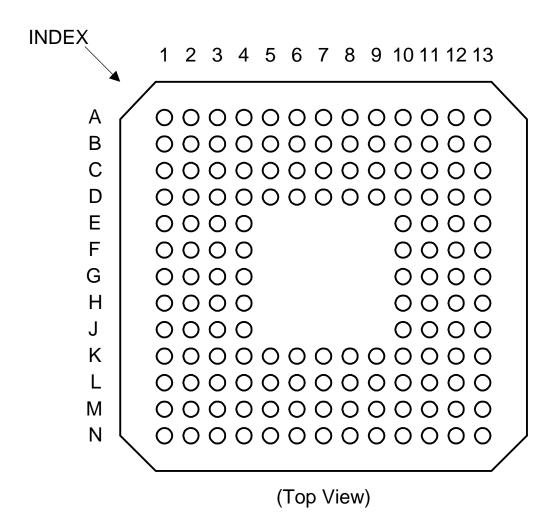

# 144 Pin - Mini BGA

# OZ6812 Mini-BGA Pin List

| BGA<br>144 | Pin Name                       | BGA<br>144 | Pin Name                   | BGA<br>144 | Pin Name    | BGA<br>144 | Pin Name                 |

|------------|--------------------------------|------------|----------------------------|------------|-------------|------------|--------------------------|

| A1         | REQ#                           | D1         | AD25                       | H3         | AD18        | L13        | D4/CAD1                  |

| A2         | D9/CAD30                       | D2         | AD27                       | H4         | AD16        | M1         | PERR#                    |

| A3         | D0/CAD27                       | D3         | GND                        | H10        | CORE_VCC    | M2         | AD15                     |

| A4         | WP/IOIS16/<br>CCLKRUN#         | D4         | AD31                       | H11        | D15/CAD8    | M3         | AD12                     |

| A5         | WAIT#/CSERR#                   | D5         | D8/CAD28                   | H12        | A10/CAD9    | M4         | PCI_VCC                  |

| A6         | GND                            | D6         | BVD2/SPKR#/LED<br>/ CAUDIO | H13        | CE1#/CCBE0# | M5         | C/BE0#                   |

| A7         | A2/CAD24                       | D7         | A0/CAD26                   | J1         | AD17        | M6         | AD4                      |

| A8         | A3/CAD23                       | D8         | CORE_VCC                   | J2         | C/BE2#      | M7         | AD1                      |

| A9         | A4/CAD22                       | D9         | VS2/CVS2                   | J3         | IRDY#       | M8         | RI_OUT/PME#              |

| A10        | A6/CAD20                       | D10        | A23/CFRAME#                | J4         | DEVSEL#     | M9         | AUX_VCC                  |

| A11        | A7/CAD18                       | D11        | A20/CSTOP#                 | J10        | D5/CAD3     | M10        | CORE_VCC                 |

| A12        | A12/CCBE2#                     | D12        | CORE_VCC                   | J11        | D6/CAD5     | M11        | VPPD0/SLATCH             |

| A13        | A22/CTRDY#                     | D13        | A18/RFU                    | J12        | D14/RFU     | M12        | VCCD1#/SMBCLK/<br>SCLK   |

| B1         | AD30                           | E1         | IDSEL                      | J13        | D7/CAD7     | M13        | D3/CAD0                  |

| B2         | GNT#                           | E2         | C/BE3#                     | K1         | FRAME#      | N1         | C/BE1#                   |

| B3         | D2/RFU                         | E3         | AD24                       | K2         | PCI_VCC     | N2         | AD13                     |

| B4         | CORE_VCC                       | E4         | AD26                       | K3         | STOP#       | N3         | AD11                     |

| B5         | BVD1/STSCHG#/<br>RI# / CSTSCHG | E10        | A14/CPERR#                 | K4         | AD14        | N4         | AD9                      |

| B6         | VS1/CVS1                       | E11        | A13/CPAR                   | K5         | AD10        | N5         | AD7                      |

| B7         | A1/CAD25                       | E12        | A8/CCBE1#                  | K6         | PCI_VCC     | N6         | AD5                      |

| B8         | REG#/CCBE3#                    | E13        | A9/CAD14                   | K7         | AD0         | N7         | AD2                      |

| B9         | A5/CAD21                       | F1         | AD22                       | K8         | SPKR_OUT#   | N8         | GND                      |

| B10        | A25/CAD19                      | F2         | AD21                       | K9         | MF5         | N9         | MF1                      |

| B11        | A24/CAD17                      | F3         | AD23                       | K10        | CD1/CCD1#   | N10        | MF2                      |

| B12        | A15/CIRDY#                     | F4         | CORE_VCC                   | K11        | GND         | N11        | MF4                      |

| B13        | WE#/CGNT#                      | F10        | A17/CAD16                  | K12        | D12/CAD4    | N12        | SUSPEND#                 |

| C1         | AD28                           | F11        | IOW#/CAD15                 | K13        | D13/CAD6    | N13        | VCCD0#/SMBDATA<br>/SDATA |

| C2         | AD29                           | F12        | A11/CAD12                  | L1         | TRDY#       |            | <u> </u>                 |

| C3         | D10/CAD31                      | F13        | GND                        | L2         | SERR#       |            |                          |

| C4         | D1/CAD29                       | G1         | AD20                       | L3         | PAR         |            |                          |

| C5         | CD2/CCD2#                      | G2         | RST#                       | L4         | GND         |            |                          |

| C6         | RDY/REQ# / CINT#               | G3         | PCI_VCC                    | L5         | AD8         |            |                          |

| C7         | SOCKET_VCC                     | G4         | PCI_CLK                    | L6         | AD6         |            |                          |

| C8         | INPACK#/CREQ#                  | G10        | IORD#/CAD13                | L7         | AD3         |            |                          |

| C9         | RESET/CRST#                    | G11        | SOCKET_VCC                 | L8         | MF0         |            |                          |

| C10        | GND                            | G12        | OE#/CAD11                  | L9         | MF3         |            |                          |

| C11        | A16/CCLK#                      | G13        | CE2#CAD10                  | L10        | MF6         |            |                          |

| C12        | A21/CDEVSEL#                   | H1         | GND                        | L11        | VPPD1       |            |                          |

| C13        | A19/CBLOCK#                    | H2         | AD19                       | L12        | D11/CAD2    |            |                          |

### Pin List Bold Text = Normal Default Pin Name

# **PCI Bus Interface Pins**

| Pin Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pin N                                                               | lumber                                                                                                                                             | Input | Туре | Power   | Drive       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|---------|-------------|

| FIII Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       | LQFP                                                                | BGA                                                                                                                                                | input | Type | Rail    | Drive       |

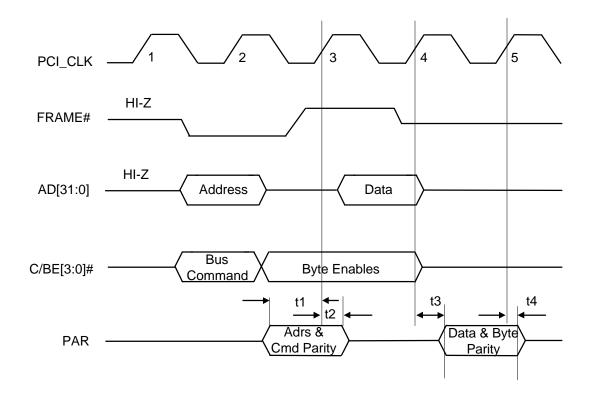

| AD[31:0]   | <b>PCI Bus Address Input / Data:</b> These pins connect to PCI bus signals AD[31:0]. A Bus transaction consists of an address phase follow by one or more data phases.                                                                                                                                                                                                                                                                                            | 3-5, 7-11, 15-<br>17, 19, 23-26,<br>38-41, 43, 45-<br>47, 49, 51-57 | D4, B1, C2-1,<br>D2, E4, D1,<br>E3, F3, F1, F2,<br>G1, H2-3, J1,<br>H4, M2, K4,<br>N2, M3, N3,<br>K5, N4, L5, N5,<br>L6, N6, M6, L7,<br>N7, M7, K7 | TTL   | I/O  | PCI_Vcc | PCI<br>Spec |

| C/BE[3:0]# | <b>PCI Bus Command / Byte Enable:</b> The command signaling and byte enables are multiplexed on the same pins. During the address phase of a transaction, C/BE[3:0]# are interpreted as the bus commands. During the data phase, C/BE[3:0]# are interpreted as byte enables. The byte enables are to be valid for the entirety of each data phase, and they indicate which bytes in the 32-bit data path are to carry meaningful data for the current data phase. | 12, 27, 37, 48                                                      | E2, J2, N1, M5                                                                                                                                     | TTL   | I/O  | PCI_Vcc | PCI<br>Spec |

| FRAME#     | <b>Cycle Frame:</b> This input indicates to the OZ6812 that a bus transaction is beginning. While FRAME# is asserted, data transfers continue. When FRAME# is de-asserted, the transaction is in its final phase.                                                                                                                                                                                                                                                 | 28                                                                  | K1                                                                                                                                                 | TTL   | I/O  | PCI_Vcc | PCI<br>Spec |

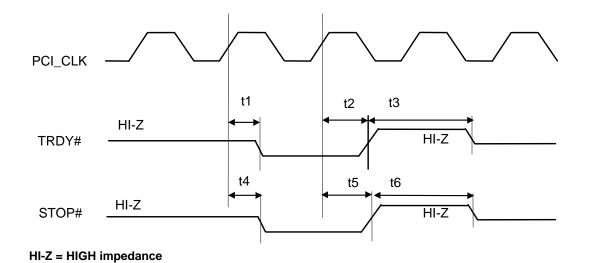

| IRDY#      | <b>Initiator Ready:</b> This input indicates the initiating agent's ability to complete the current data phase of the transaction. IRDY# is used in conjunction with TRDY#.                                                                                                                                                                                                                                                                                       | 29                                                                  | J3                                                                                                                                                 | TTL   | I/O  | PCI_Vcc | PCI<br>Spec |

| TRDY#      | <b>Target Ready:</b> This output indicates target Agent's the OZ6812's ability to complete the current data phase of the transaction. TRDY# is used in conjunction with IRDY#.                                                                                                                                                                                                                                                                                    | 31                                                                  | L1                                                                                                                                                 | TTL   | I/O  | PCI_Vcc | PCI<br>Spec |

| STOP#      | <b>Stop:</b> This output indicates the current target is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                   | 33                                                                  | КЗ                                                                                                                                                 | TTL   | I/O  | PCI_Vcc | PCI<br>Spec |

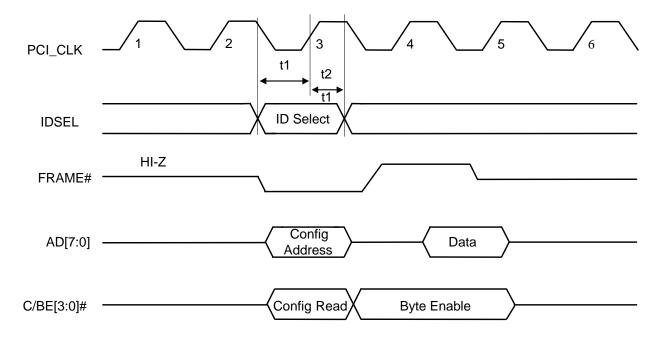

| IDSEL      | <b>Initialization Device Select:</b> This input is used as<br>a chip select during configuration read and write<br>transactions. This is a point-to-point signal.<br>IDSEL can be used as a chip select during<br>configuration read and write transactions.                                                                                                                                                                                                      | 13                                                                  | E1                                                                                                                                                 | TTL   | I    | PCI_Vcc | PCI<br>Spec |

| DEVSEL#    | <b>Device Select:</b> This output is driven active LOW when the PCI address is recognized as supported, thereby acting as the target for the current PCI cycle. The Target must respond before timeout occurs or the cycle will terminate.                                                                                                                                                                                                                        | 32                                                                  | J4                                                                                                                                                 | TTL   | I/O  | PCI_Vcc | PCI<br>Spec |

| PERR#      | <b>Parity Error:</b> The output is driven active LOW when a data parity error is detected during a write phase.                                                                                                                                                                                                                                                                                                                                                   | 34                                                                  | M1                                                                                                                                                 | -     | то   | PCI_Vcc | PCI<br>Spec |

| SERR#      | <b>System Error:</b> This output is driven active LOW to indicate an address parity error.                                                                                                                                                                                                                                                                                                                                                                        | 35                                                                  | L2                                                                                                                                                 | -     | ТО   | PCI_Vcc | PCI<br>Spec |

| Din Nomo | Description                                                                                                                                                                                                                                                  | Pin N | Innut | Tuno  | Power | Drive   |             |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|---------|-------------|

| Pin Name | Description -                                                                                                                                                                                                                                                | LQFP  | BGA   | Input | Туре  | Rail    | Drive       |

| PAR      | <b>Parity:</b> This pin generates PCI parity and ensures<br>even parity across AD[31:0] and C/BE[3:0]#.<br>During the address phase, PAR is valid after one<br>clock. With data phases, PAR is stable one clock<br>after a write or read transaction.        | 36    | L3    | TTL   | I/O   | PCI_Vcc | PCI<br>Spec |

| PCI_CLK  | <b>PCI Clock:</b> This input provides timing for all transactions on the PCI bus to and from the OZ6812. All PCI bus signals, except RST#, are sampled and driven on the rising edge of PCI_CLK. This input can be operated at frequencies from 0 to 33 MHz. | 21    | G4    | -     | 1     | PCI_Vcc | -           |

| RST#     | <b>Device Reset:</b> This input is used to initialize all registers and internal logic to their reset states and place most OZ6812 pins in a HIGH-impedance state.                                                                                           | 20    | G2    | -     | I     | AUX_Vcc | -           |

| GNT#     | Grant : This signal indicates that access to the bus has been granted.                                                                                                                                                                                       | 2     | B2    | TTL   | I     | PCI_Vcc | PCI<br>Spec |

| REQ#     | <b>Request</b> : This signal indicates to the arbiter that the OZ6812 requests use of the bus.                                                                                                                                                               | 1     | A1    | -     | то    | PCI_Vcc | PCI<br>Spec |

# Power Control and General Interface Pins

| Pin Name        | Description                                                                                                                                                                                                                                                                                                                                               | Pin N                  | umber                          | Innut | Turne | Power   | Drive |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------|-------|-------|---------|-------|

| Pin Name        | Description                                                                                                                                                                                                                                                                                                                                               | LQFP                   | BGA                            | Input | Туре  | Rail    | Drive |

| RI_OUT/<br>PME# | <ul> <li>Ring Indicate Out: This pin is Ring Indicate when the following occurs while O<sub>2</sub> Mode Control B Register (index 2Eh) bit 7 is set to 1:</li> <li>1) Power Control (Index+02h) bit 7 set to 1</li> <li>2) Interrupt and General Control (Index+03h) bit 7 set to 1</li> <li>3) PCI O2Micro Control 2 (Offset: D4h) bit X = 0</li> </ul> | 59                     | M8                             | -     | то    | Aux_Vcc | 4mA   |

|                 | <b>Power Management Event:</b> A power management event is the process by which the OZ6812 can request a change of its power consumption state. Usually, a PME occurs during a request to change from a power saving state to the fully operational state.                                                                                                |                        |                                |       |       |         |       |

| SPKR_OUT#       | <b>Speaker Output:</b> This output can be used to support PCCard audio output. See O2 Mode E Register (Index + 3Eh), bit 1.                                                                                                                                                                                                                               | 62                     | K8                             | TTL   | I/O   | Aux_Vcc | 12mA  |

| MF[6:0]         | <b>Multifunction Terminal [6:0]</b> : See PCI Multifunction MUX Register (Offset:08h).                                                                                                                                                                                                                                                                    | 69-67, 65-64,<br>61-60 | L10, K9, N11,<br>L9, N10-9, L8 | TTL   | I/O   | Aux_Vcc | 12mA  |

| SUSPEND#        | <b>Suspend:</b> This signal is used to protect the internal registers from clearing when the PCI RST# signal is asserted. When low, this signal is used to mask the PCI RESET during suspend. This pin can be used during suspend to prevent controller reset.                                                                                            | 70                     | N12                            | TTL   | I     | Aux_Vcc | -     |

| Dia Mara                     | Description                                                                                                                                                                                                                                        | Pin N | umber |       | <b>T</b> | Power   | Dation |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|----------|---------|--------|

| Pin Name                     | Description                                                                                                                                                                                                                                        | LQFP  | BGA   | Input | Туре     | Rail    | Drive  |

| VPPD0<br>/SLATCH             | <b>VPPD0:</b> This power input is used with parallel power control chip                                                                                                                                                                            | 71    | M11   | TTL   | I/O      | Aux_Vcc | 12mA   |

|                              | <b>SLATCH:</b> This output controls a serial interface power control chip.                                                                                                                                                                         |       |       |       |          |         |        |

| VPPD1                        | <b>VPPD1:</b> This power input is used a parallel power interface chip.                                                                                                                                                                            | 72    | L11   | -     | то       | Aux_Vcc | 12mA   |

| VCCD0#<br>/SMBDATA<br>/SDATA | <b>VCCD0#</b> : Rail power inputs for use with a parallel power control chip.                                                                                                                                                                      | 73    | N13   | TTL   | I/O      | Aux_Vcc | 12mA   |

|                              | <b>SMBus Data:</b> This pin serves as a bi-directional data pin when used with the SMBus socket power control chip.                                                                                                                                |       |       |       |          |         |        |

|                              | <b>Serial Data:</b> This pin serves as output DATA pin when used with a serial interface of serial power control chip.                                                                                                                             |       |       |       |          |         |        |

| VCCD1#<br>/SMBCLK<br>/SCLK   | <b>VCCD1#:</b> Rail power inputs for use with a parallel power control chip.                                                                                                                                                                       | 74    | M12   | TTL   | I/O      | Aux_Vcc | 12mA   |

|                              | <b>SMBus Clock:</b> This pin serves as the clock when used with a SMBus socket power control chip.                                                                                                                                                 |       |       |       |          |         |        |

|                              | Serial Clock: The input is used as a reference<br>clock (10-100kHz, usually 32kHz) to control a<br>serial power control chips. By setting PCI<br>O2Micro Control 2 register (Offset:D4h) bit 13 to<br>1, SCLK is an output. Default is input mode. |       |       |       |          |         |        |

# OZ6812 Slot Power Table

| VCCD0# | VCCD1# | VPPD0 | VPPD1 | Slot_VCC | Slot_VPP         |

|--------|--------|-------|-------|----------|------------------|

| 0      | 1      | 0     | 0     | 5        | Switch Dependent |

| 0      | 1      | 0     | 1     | 5        | 5                |

| 0      | 1      | 1     | 0     | 5        | 12               |

| 0      | 1      | 1     | 1     | 5        | Switch Dependent |

| 1      | 0      | 0     | 0     | 3.3      | Switch Dependent |

| 1      | 0      | 0     | 1     | 3.3      | 3.3              |

| 1      | 0      | 1     | 0     | 3.3      | 12               |

| 1      | 0      | 1     | 1     | 3.3      | Switch Dependent |

# PCCard Socket Interface Pins

Refer to PCI Bus Interface pin descriptions for details on CardBus function. **EXCEPTIONS: CCD[2:1]#, CAUDIO, CSTSCHG, CVS[2:1]**

| Pin Name                 | Description                                                                                                                                                                                                                                                                                                                                      | Pin N    | umber    | Innut | Tuno       | Power          | Drive            |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------|------------|----------------|------------------|

| Pin Name                 | Description                                                                                                                                                                                                                                                                                                                                      | LQFP     | BGA      | Input | Туре       | Rail           | Drive            |

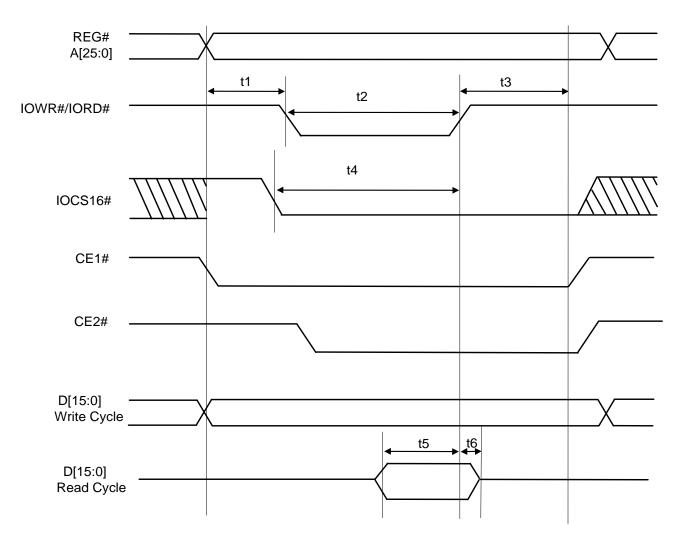

| REG#/<br>CCBE3#          | <b>Register Access:</b> During PCCard memory cycles,<br>this output chooses between Attribute and Common<br>Memory. During I/O cycles for non-DMA transfers,<br>this signal is active (low). During ATA mode, this<br>signal is always inactive. For DMA cycles on the<br>OZ6812 to a DMA-capable card, REG# becomes<br>DACK to the PCMCIA card. | 125      | B8       | TTL   | I/O        | Socket<br>_Vcc | CardBus<br>spec. |

|                          | CardBus Command Byte Enable: In CardBus mode, this pin is the CCBE3#.                                                                                                                                                                                                                                                                            |          |          |       |            |                |                  |

| A[25:24]/<br>CAD[19, 17] | Address: PCCard socket address 25:24 outputs.<br>CardBus Address/Data: CardBus mode, these pins<br>are the CAD bits 19 and 17.                                                                                                                                                                                                                   | 116, 113 | B10, B11 | TTL   | I/O        | Socket<br>_Vcc | CardBus<br>spec. |

| A23/<br>CFRAME#          | Address: PCCard socket address 23 output.<br>CardBus Frame: In CardBus mode, this pin is the<br>CFRAME# signal.                                                                                                                                                                                                                                  | 111      | D10      | TTL   | I/O        | Socket<br>_Vcc | CardBus spec.    |

| A22/<br>CTRDY#           | Address: PCCard socket address 22 output.<br>CardBus Target Ready: In CardBus mode, this pin<br>is the CTRDY# signal.                                                                                                                                                                                                                            | 109      | A13      | TTL   | I/O-<br>PU | Socket<br>_Vcc | CardBus<br>spec. |

| A21/<br>CDEVSEL#         | Address: PCCard socket address 21 output.<br>CardBus Device Select: In CardBus mode, this pin<br>is the CDEVSEL# signal.                                                                                                                                                                                                                         | 107      | C12      | TTL   | I/O-<br>PU | Socket<br>_Vcc | CardBus spec.    |

| A20/<br>CSTOP#           | Address: PCCard socket address 20 output.<br>CardBus Stop: In CardBus mode, this pin is the<br>CSTOP# signal.                                                                                                                                                                                                                                    | 105      | D11      | TTL   | I/O-<br>PU | Socket<br>_Vcc | CardBus spec.    |

| A19/<br>CBLOCK#          | Address: PCCard socket address 19 output.<br>CardBus Lock: In CardBus mode, this signal is the<br>CBLOCK# signal used for locked transactions.                                                                                                                                                                                                   | 103      | C13      | TTL   | I/O-<br>PU | Socket<br>_Vcc | CardBus<br>spec. |

| A18/<br>RFU              | Address: PCCard socket address 18 output.<br>Reserved: In CardBus mode, this pin is reserved for future use.                                                                                                                                                                                                                                     | 100      | D13      | TTL   | то         | Socket<br>_Vcc | CardBus<br>spec. |

| A17/<br>CAD16            | Address: PCCard socket address 17 output.<br>CardBus Address/Data: In CardBus mode, this pin<br>is the CAD bit 16.                                                                                                                                                                                                                               | 98       | F10      | TTL   | I/O        | Socket<br>_Vcc | CardBus<br>spec. |

| A16/<br>CCLK#            | Address: PCCard socket address 16 output.<br>CardBus Clock: In CardBus mode, this pin supplies<br>the clock to the inserted card.                                                                                                                                                                                                                | 108      | C11      | TTL   | I/O        | Socket<br>_Vcc | CardBus<br>spec. |

| Pin Name                      | Description                                                                                                                |                                     | umber                                    | Input | Туре       | Power          | Drive            |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------|-------|------------|----------------|------------------|

| A15/                          | Address: PCCard socket address 15 output.                                                                                  | LQFP<br>110                         | BGA<br>B12                               | TTL   | 1/0-       | Rail<br>Socket | CardBus          |

| CIRDY#                        | <b>CardBus Initiator Ready:</b> In CardBus mode, this pin is the CIRDY# signal.                                            | 110                                 | DIZ                                      |       | PU         | _Vcc           | spec.            |

| A14/<br>CPERR#                | Address: PCCard socket address 14 output.<br>CardBus Parity Error: CardBus mode, this pin is                               | 104                                 | E10                                      | TTL   | I/O-<br>PU | Socket<br>_Vcc | CardBus spec.    |

|                               | the CPERR# signal.                                                                                                         |                                     |                                          |       |            |                |                  |

| A13/<br>CPAR                  | Address: PCCard socket address 13 output.<br>CardBus Parity:b In CardBus mode, this pin is the                             | 101                                 | E11                                      | TTL   | I/O        | Socket<br>_Vcc | CardBus spec.    |

| A12/<br>CCBE2#                | CPAR signal.<br>Address: PCCard socket address 12 output.                                                                  | 112                                 | A12                                      | TTL   | I/O        | Socket<br>_Vcc | CardBus spec.    |

|                               | <b>CardBus Command/Byte Enable:</b> In CardBus mode, this pin is the CCBE2# signal.                                        |                                     |                                          |       |            |                |                  |

| A[11:9]/<br>CAD               | Address: PCCard socket address 11:9 output.<br>CardBus Address/Data: In CardBus mode, these                                | 95, 89, 97                          | F12,H12,<br>E13                          | TTL   | I/O        | Socket<br>_Vcc | CardBus spec.    |

| [12,9,14]                     | pin are the CAD bits 12, 9 and 14.                                                                                         |                                     |                                          |       |            |                |                  |

| A8/<br>CCBE1#                 | Address: PCCard socket address 8 output.<br>CardBus Command/Byte Enable: In CardBus                                        | 99                                  | E12                                      | TTL   | I/O        | Socket<br>_Vcc | CardBus spec.    |

|                               | mode, this pin is the CCBE1# signal.                                                                                       |                                     |                                          |       |            |                |                  |

| A[7:0]/<br>CAD[18]<br>[20:26] | Address: PCCard socket address 7:0 outputs.<br>CardBus Address/Data: In CardBus mode, these                                | 115, 118,<br>120, 121,<br>124, 127, | A11-10, B9,<br>A9-7, B7,<br>D7           | TTL   | I/O        | Socket<br>_Vcc | CardBus<br>spec. |

| D15/                          | pins are the CAD bits 18 and 20:26.<br><b>Data:</b> PCCard socket I/O data bit 15.                                         | 128, 129<br>87                      | H11                                      | TTL   | I/O        | Socket         | CardBus          |

| CAD8                          | CardBus Address/Data: In CardBus mode, this pin is the CAD bit 8.                                                          |                                     |                                          |       |            | _Vcc           | spec.            |

| D14/<br>RFU                   | Data: PCCard socket I/O data bit 14.<br>Reserved: In CardBus mode, this pin is reserved for future use.                    | 84                                  | J12                                      | TTL   | I/O        | Socket<br>_Vcc | CardBus<br>spec. |

| D[13:3]/<br>CAD[6, 4, 2,      | Data: PCCard socket I/O data lbits 13:3.                                                                                   | 82, 80, 77,<br>144, 142,            | K13-12,<br>L12, C3,                      | TTL   | I/O        | Socket<br>_Vcc | CardBus spec.    |

| 31, 30, 28, 7,<br>5, 3, 1, 0] | <b>CardBus Address/Data:</b> In CardBus mode, this pin is the CAD bit 6 4, 2, 31, 30, 28, 7, 5, 3, 1, and 0, respectively. | 140, 85, 83,<br>81, 79, 76          | A2, D5,<br>J13, J11,<br>J10, L13,<br>M13 |       |            |                | 5000             |

| D2/<br>RFU                    | Data: PCCard socket I/O data bit 2.                                                                                        | 143                                 | B3                                       | TTL   | I/O        | Socket<br>_Vcc | CardBus spec.    |

|                               | <b>Reserved:</b> In CardBus mode, this pin is reserved for future use.                                                     |                                     |                                          |       |            |                |                  |

| D[1:0]/<br>CAD[29,27]         | Data: PCCard socket I/O data bits 1:0.                                                                                     | 141, 139                            | C4, A3                                   | TTL   | I/O        | Socket<br>_Vcc | CardBus spec.    |

|                               | <b>CardBus Address/Data:</b> In CardBus mode, these pins are the CAD bits 29 and 27, respectively.                         |                                     |                                          |       |            |                |                  |

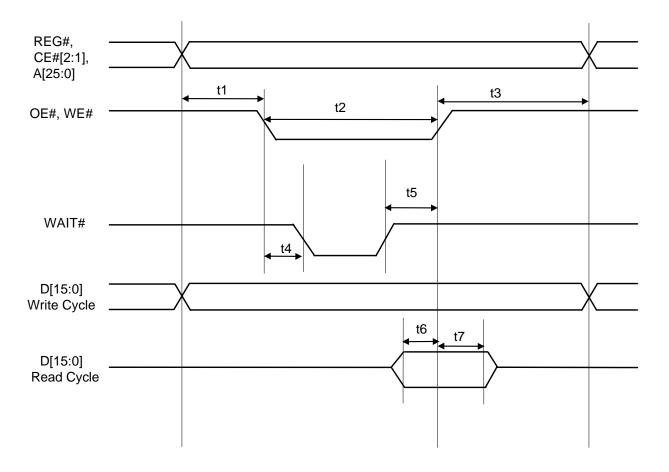

| OE#/<br>CAD11                 | <b>Output Enable</b> : This output goes active (low) to indicate a memory read from the OZ6812 to PCCard.                  | 92                                  | G12                                      | TTL   | I/O        | Socket<br>_Vcc | CardBus<br>spec. |

|                               | CardBus Address/Data: In CardBus mode, this pin is the CAD bit 11.                                                         |                                     |                                          |       |            |                |                  |

| WE#/<br>CGNT#                 | Write Enable: This output goes active (low) to indicate a memory write from the OZ6812 to the PCCard socket.               | 106                                 | B13                                      | TTL   | то         | Socket<br>_Vcc | CardBus<br>spec. |

|                               | CardBus Grant: In CardBus mode, this pin is the CGNT# signal.                                                              |                                     |                                          |       |            |                |                  |

| Pin Name                    | Description                                                                                                                                                                                                                                        | Pin Nu  | umber   | Innut | Type             | Power          | Drive            |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-------|------------------|----------------|------------------|

| rin Name                    | •                                                                                                                                                                                                                                                  | LQFP    | BGA     | Input | Туре             | Rail           | -                |

| IORD#/<br>CAD13             | <b>I/O Read</b> : This output goes active (low) for I/O reads from the OZ6812 to the socket.                                                                                                                                                       | 93      | G10     | TTL   | I/O              | Socket<br>_Vcc | CardBus spec.    |

|                             | CardBus Address/Data: In CardBus mode, this pin is the CAD bit 13.                                                                                                                                                                                 |         |         |       |                  |                |                  |

| IOW#/<br>CAD15              | <b>I/O Write</b> : This output goes active (low) for I/O writes from the OZ6812 to the socket.                                                                                                                                                     | 96      | F11     | TTL   | I/O              | Socket<br>_Vcc | CardBus<br>spec. |

|                             | CardBus Address/Data: In CardBus mode, this pin is the CAD bit 15.                                                                                                                                                                                 |         |         |       |                  |                |                  |

| WP/<br>IOIS16#/<br>CCLKRUN# | Write Protect / I/O is 16-Bit: In Memory mode,<br>this input is indicates the status of the write<br>protect switch on the PCCard. In I/O mode, this<br>input indicates the size of current data transfer on<br>the PCCard.                        | 136     | A4      | TTL   | I/O-PU           | Socket<br>_Vcc | CardBus<br>spec. |

|                             | <b>CardBus Clock Run:</b> In CardBus mode, this pin<br>is the CCLKRUN# signal, which starts and stops<br>the CardBus CCLK. To enable the CLKRUN#<br>signal, ExCA register 3Bh bit[3:2] must be<br>enabled.                                         |         |         |       |                  |                |                  |

| INPACK#/<br>CREQ#           | <b>Input Acknowledge:</b> The INPACK# function is<br>not applicable in PCI bus environments. This pin<br>is provided for Legacy card compatibility.                                                                                                | 123     | C8      | -     | I-PU             | Socket<br>_Vcc | CardBus<br>spec. |

|                             | <b>CardBus Request:</b> In CardBus mode, this pin is the CREQ# signal.                                                                                                                                                                             |         |         |       |                  |                |                  |

| RDY/IREQ#/<br>CINT#         | <b>Ready / Interrupt Request:</b> In Memory mode, this input indicates that the card is ready or busy. In I/O mode, this input indicates a card interrupt request.                                                                                 | 132     | C6      | -     | I-PU             | Socket<br>_Vcc | CardBus<br>spec. |

|                             | <b>CardBus Interrupt:</b> In CardBus mode, this pin is the CINT# signal. This signal is active-low and level-sensitive.                                                                                                                            |         |         |       |                  |                |                  |

| WAIT#/<br>CSERR#            | Wait: This pin is driven by the PCCard to delay completion of the current cycle.                                                                                                                                                                   | 133     | A5      | TTL   | I-PU             | Socket<br>_Vcc | CardBus spec.    |

|                             | <b>CardBus System Error:</b> In CardBus mode, this pin is the CSERR# signal.                                                                                                                                                                       |         |         |       |                  |                |                  |

| CD[2:1]/<br>CCD[2:1]#       | <b>Card Detect</b> : These inputs indicate a card is present in the socket. They are internally pulled high to AUX_VCC.                                                                                                                            | 137, 75 | C5, K10 | TTL   | I-PU-<br>Schmitt | Aux_Vcc        | CardBus<br>spec. |

|                             | <b>CardBus Card Detect:</b> In CardBus mode, these inputs are used with CVS[2:1] to detect presence and type of card.                                                                                                                              |         |         |       |                  |                |                  |

| CE2#/<br>CAD10              | <b>Card Enable 2:</b> This pin is driven low to control byte/word card access. CE2# enables odd-numbered address bytes.                                                                                                                            | 91      | G13     | TTL   | I/O              | Socket<br>_Vcc | CardBus<br>spec. |

|                             | CardBus Address/Data: In CardBus mode, this pin is the CAD bit 10.                                                                                                                                                                                 |         |         |       |                  |                |                  |

| CE1#/<br>CCBE0#             | <b>Card Enable 1:</b> This pin is driven low to control byte/word card access. CE1# enables even-<br>numbered address bytes. When configured for 8-<br>bit cards, CE1# is active and A0 is used to indicate access of odd- or even-numbered bytes. | 88      | H13     | TTL   | I/O              | Socket<br>_Vcc | CardBus<br>spec. |

|                             | CardBus Command/Byte Enable: In CardBus mode, this pin is the CCBEO# signal.                                                                                                                                                                       |         |         |       |                  |                |                  |

| Dia Nama                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pin Nu   | ımber   |       | Turne  | Power          | Duita            |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|-------|--------|----------------|------------------|

| Pin Name                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LQFP     | BGA     | Input | Туре   | Rail           | Drive            |

| RESET/<br>CRST#                   | <b>Reset:</b> This active high output resets the card.<br>To prevent reset glitches, this signal is high-<br>impedance unless a card is seated in the<br>socket, card power is applied, and the card's<br>interface signals are enabled.<br><b>CardBus Reset:</b> In CardBus mode, this pin is<br>the CRST# output                                                                                                                                                                                         | 119      | C9      | TTL   | то     | Socket<br>_Vcc | CardBus<br>spec. |

| BVD2/SPKR#/                       | the CRST# output.<br>Battery Voltage Detect 2 / Speaker / LED: In                                                                                                                                                                                                                                                                                                                                                                                                                                          | 134      | D6      |       | I-PU   | Socket         |                  |

| LED / CAUDIO                      | Memory mode, this input serves as the BVD2<br>(battery warning status) input. In I/O mode, this<br>input can be configured as the card's SPKR#<br>audio input or drive-active LED input.<br><b>CardBus Audio:</b> In CardBus mode, this pin is<br>the CAUDIO input.                                                                                                                                                                                                                                        | 134      |         |       |        | _Vcc           |                  |

| BVD1/<br>STSCHG#/RI#<br>/ CSTSCHG | Battery Voltage Detect 1 / Status Change /<br>Ring Indicate: In Memory mode, this is the<br>BVD1 (battery-dead status) input. In I/O mode,<br>this is the STSCHG# input indicating that the<br>card's internal status has changed, or the ring<br>indicate input for wakeup-on-ring system power<br>management support. See bit 7 of the Interrupt<br>and General Control register (03h).<br>CardBus Status Change: In CardBus mode,<br>this pin is the CSTSCHG. This pin can be used<br>to generate PME#. | 135      | B5      | -     | I-PU   | Socket<br>_Vcc | -                |

| VS[2:1]/<br>CVS[2:1]              | Voltage Sense: These pins are used in<br>conjunction with CD[2:1] to determine the type<br>and voltage of a card. These pins are internally<br>pulled high to AUX_VCC. See Table 1.<br>CardBus Voltage Sense: In CardBus mode,<br>these pins are the CVS[2:1] pins.                                                                                                                                                                                                                                        | 117, 131 | D9, B6  | TTL   | I/O-PU | Aux_Vcc        | CardBus<br>spec. |

| SOCKET_VCC                        | <b>Socket Power:</b> These pins are the power rail input for the socket interface control logic. These pins can be 0, 3.3, or 5 V,. The socket interface outputs will operate at the voltage applied to these pins.                                                                                                                                                                                                                                                                                        | 90, 126  | G11, C7 | -     | PWR    | -              | -                |

# Power, Ground, and Reserved Pins

| Pin Name | Description                                                                                                                                                                                                                             | Pin Nu                                | ımber                                      | Innut | Tune | Power | Drive |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------|-------|------|-------|-------|

| Pin Name | Description                                                                                                                                                                                                                             | LQFP                                  | BGA                                        | Input | Туре | Rail  | Drive |

| Aux_VCC  | Auxiliary VCC: This pin is connected to the system's 3.3/5V power supply. For the device to 5V tolerant, connect to +5V power.                                                                                                          | 63                                    | M9                                         | -     | PWR  | -     | -     |

| CORE_VCC | <b>CORE_VCC:</b> This pin provides power to the core circuitry of the OZ6812. It must be connected to a 3.3V power supply.                                                                                                              | 14, 66, 86,<br>102, 122,<br>138       | F4, M10,<br>H10, D12,<br>D8, B4            | -     | PWR  | -     | -     |

| PCI_VCC  | <b>PCI Bus VCC:</b> These pins can be connected to<br>either a 3.3V or5V power supply. The PCI bus<br>interface will operate at the voltage applied to<br>these pins, independent of the voltage applied<br>to other OZ6812 pin groups. | 18, 30, 44,<br>50                     | G3, K2,<br>M4, K6                          | -     | PWR  | -     | -     |

| GND      | System Ground                                                                                                                                                                                                                           | 6, 22, 42,<br>58, 78, 94,<br>114, 130 | D3, H1,<br>L4, N8,<br>K11, F13,<br>C10, A6 | -     | GND  | -     | -     |

# Legend

| I/O Type     | Description                                         | 1 | Power Rail |                   |

|--------------|-----------------------------------------------------|---|------------|-------------------|

| 1            | Input Pin                                           |   | 1          | AUX_VC            |

| I-PU         | Input pin with internal pull-up                     |   | 2          | SOCKET            |

| I-PU Schmitt | Input pin with internal pull-up and Schmitt trigger |   | 3          | PCI_VCC<br>supply |

| 0            | Output                                              |   |            |                   |

| OD           | Open-drain                                          |   | 4          | CORE_V            |

| ТО           | Tri-state output                                    |   |            |                   |

| TO-PU        | Tri-state output with internal pull-up              |   |            |                   |

| OD-PU        | Open-drain output with internal pull-up             |   |            |                   |

| PWR          | Power pin                                           |   |            |                   |

| Power Rail | Source of Output's Power                              |

|------------|-------------------------------------------------------|

| 1          | AUX_VCC: outputs powered from AUX_VCC                 |

| 2          | SOCKET_VCC: outputs powered from the socket           |

| 3          | PCI_VCC: outputs powered from PCI bus power<br>supply |

| 4          | CORE_VCC: outputs powered from the CORE_VCC           |

# FUNCTIONAL INFORMATION

## **1. INTRODUCTION TO OZ6812**

#### 1.1. Architectural Overview

O2Micro's OZ6812 is the solution for today's notebook PCs. It interfaces directly to the PC card socket and PCI bus without additional buffers, thus requiring minimal PC board real estate. It is a bridge between the PCI local bus and the PCMCIA socket, supporting both 16-bit PCCard and 32-bit CardBus devices. The OZ6812 provides a 32-bit point-to-point connection between the card socket and CardBus bridge, enabling a maximum theoretical throughput of 132MB/second. The OZ6812's core logic is powered at 3.3V to minimize power dissipation.

The OZ6812 allows PC socket insertion of memory and I/O devices as exchangeable peripherals. Five programmable memory windows and 2 programmable I/O windows are available to map inserted PC cards into system memory and I/O space. PC cards may have both attribute and common memory. Attribute memory indicates the PC Card's capabilities of the PC Card to host software and to allow host software to change configuration. Common memory can be used by host software for any purpose (flash file system, system memory, floppy emulation, etc.). I/O PC Cards, such as Modem and LAN Cards, are supported as if they were I/O devices on the system motherboard.

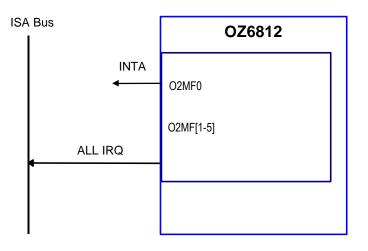

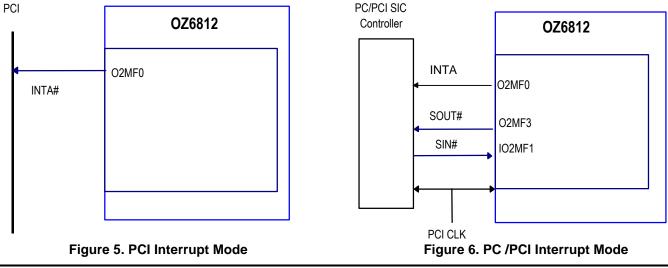

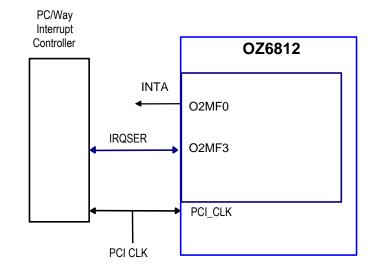

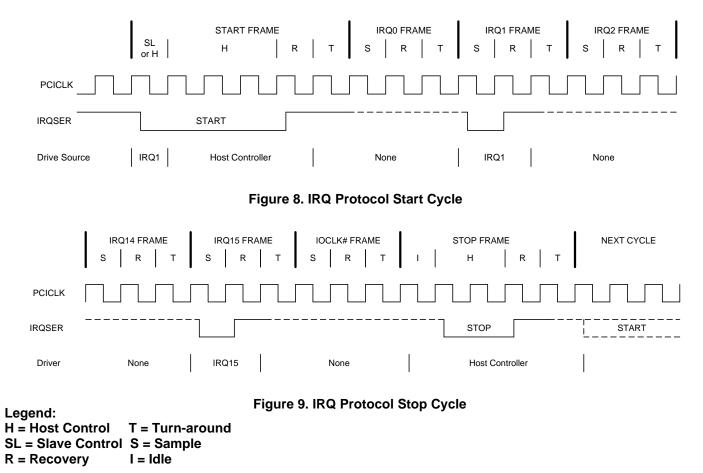

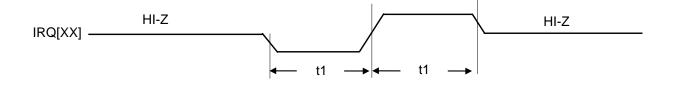

PC Card I/O device interrupts need not be limited to PCI interrupts, and each generated interrupt can be steered by the OZ6812 to a variety of system interrupts. The OZ6812 can notify the host system via interrupts when an event such as card status change (CSC) or interrupts from the PC Card occur. Both CSC and functional interrupts can be individually masked and routed to the system interrupt controller via PCI-style, ISA type, or serialized IRQ protocol.

The OZ6812 also has a flexible interface to the socket power control device. It establishes either a parallel or serial communication protocol and communicates in conventional parallel mode or three possible serial modes, standard external serial hardware, or System Bus Management mode.

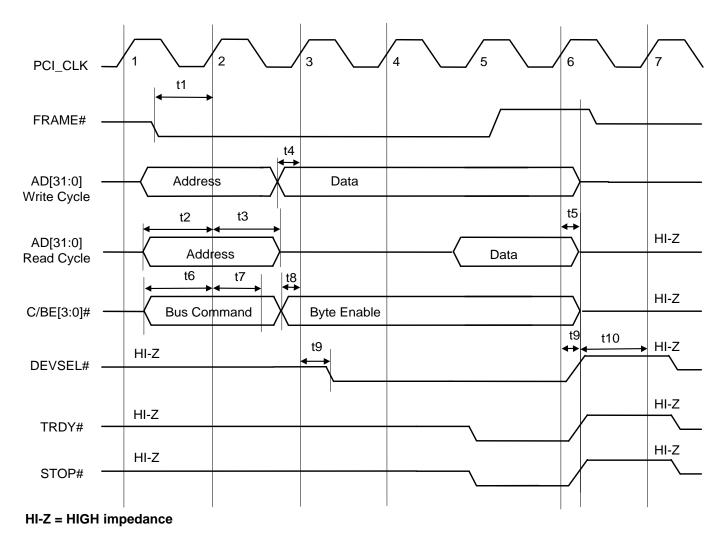

#### 1.2. PCI Interface

The OZ6812 employs the same basic transaction protocol as the PCI bus. See Appendix 1 for a comparison of CardBus to PCI bus. All OZ6812 CardBus bus transactions are synchronized to the CCLK# signal and consist of an address phase followed by one or more data phases. Each address phase is one CCLK# in duration while each data phase has a minimum duration of one CCLK#. The number of data phases depends on how many data transfers take place during the overall burst transfer. A wait state inserted in a data phase will extend the data phase by an additional CCLK#. The OZ6812 responds as a PCI target device to PCI bus cycles decoded from the address phase of each cycle. Refer to a PCI reference book such as "PCI Hardware and Software Architecture and Design" for valid PCI bus cycle types and their encoding on the 4-bit C/BE bus during the address phase of a bus cycle. The most common PCI bus commands are read and write cycles to memory, I/O, and configuration address spaces.

#### 1.3. Configuration Address Space

Like all PCI devices, the OZ6812 has configuration registers which must be programmed during system initialization. This key feature enables Plug and Play capability. The ability to identify the OZ6812 and dynamically assign system resources helps optimize system memory and I/O address space maps, avoiding system resource conflicts.

The OZ6812 is configured essentially in the same manner as any other device residing on the PCI bus. It is the OS software's responsibility to scan the PCI bus, and detect and configure the present devices. The OZ6812 is configured during the power-up sequence before recognizing PCCard installation and PCMCIA software notification that a PCCard is present.

Configuring the CardBus card is the PCMCIA software's responsibility. When a PCCard is inserted into a socket, the OZ6812 detects its presence and generates an interrupt to notify PCMCIA configuration software (client driver, Card Services and Socket Services). This software will then apply appropriate power to the socket and configure the PC Card and OZ6812 socket interface.

The PCI local bus specification defines two types of PCI configuration read and write cycles: type 0 and type 1. Type 0 configuration cycles are intended for devices on the main PCI bus, while type 1 configuration cycles are intended for devices residing on the CardBus socket bus. The difference between these two types is the PCI address AD bus encoding during the address phase of the cycle. The address AD bus encoding during the address phase of a type 0 configuration cycle, AD[10:8] selects the OZ6812. The contents of AD[7:2] accesses the configuration register. The OZ6812 claims Type 0 configuration cycles when its IDSEL pin is asserted during a configuration access cycle.

Type 1 configuration cycles are intended for PCI devices residing on either of the CardBus socket interfaces with each assigned their own CardBus bus number. The OZ6812 will claim Type 1 configuration cycles based on the destination bus number embedded in the configuration cycle address phase. The destination bus number encoded in the AD bus is compared to the values programmed in the OZ6812 configuration registers; PCI bus number (18h), CardBus bus number (19h), and subordinate bus number (1Ah). It is the responsibility of the PCI operating system to program these registers with the proper bus hierarchy, they are 00h by default.

If the socket is either empty or occupied by a 16-bit PC Card, type 1 cycles are not passed to that socket, regardless of the programming of configuration registers 18h-1Ah. The OZ6812 never issues PCI configuration read or write cycles on the PCI bus as a PCI bus master.

#### 1.4. PCMCIA Socket Interface

All PC Cards, 16-bit and CardBus, communicate with the OZ6812 through a 68 pin PCMCIA/JEIDA socket interface through 60 signals and 8 power pins. The power pin definitions remain unchanged for both types of PC Cards, with the only difference in signal pin definition.

The OZ6812 can directly support one PC card socket, with an option to allow up to eight OZ6812 devices per system. The OZ6812 supports two PC card types (either memory or I/O) interchangeably. It accomplishes this by multiplexing some of the static signals that are defined differently for memory and I/O PC cards. These signals are configured appropriately by accessing the PC card's configuration registers.

#### 1.5. Memory and I/O Window Mapping

Memory address mappings for the OZ6812 bridge are on 4K byte boundaries with a minimum mapping of 4 Kbytes. OZ6812 may be mapped anywhere within the address space assigned to the bridge. The OZ6812 provides two memory base and limit register pairs which may be used for mapping memory mapped I/O or prefetchable memory space.

Two I/O mapping register pairs are provided for each socket, allowing some fragmenting of I/O space on a card and interleaving of I/O space with other I/O devices.

Multiple PC cards in a system can conflict if they try to utilize the same system memory and I/O range. The OZ6812 allows mapping of each PC card into separate memory and I/O ranges through the use of 5 programmable memory windows and 2 programmable I/O windows for 16-bit PC cards, or through two memory or I/O windows for 32-bit CardBus cards. This function avoids system configuration conflicts. The OZ6812 has 5 memory windows with memory start address, end address, offset address and upper address register to select 16-Mbyte page.

The OZ6812 provides memory paging, memory address mapping for both PC card attribute and common memory, and I/O address mapping. The OZ6812 includes registers allowing access to the card information structure and card configuration registers within the attribute memory described by the PCMCIA/JEIDA PC Card Standard.

#### 1.6. Zoomed Video Port

The Zoomed Video (ZV) Port provides a low-cost functionality for direct video data transfer from a PC Card to the VGA frame buffer. This uni-directional bus enables the transfer of uninterrupted video data at rates up to 30 frames per second without loading the system PCI bus. Both video and audio data are transferred real-time with minimal CPU intervention. The PC Card transfers audio data to the host system using Pulse Code Modulation (PCM) in a serial I2S format. Video data is transferred by the ZV port, in compliance with CCIR601 timing, enabling direct interfacing with industry standard video graphic devices.

#### 1.7. DVD Enhanced ZV PORT Offset D0h

The ZV port specification was originally developed with ISA MPEG1 data rates in mind. Today, DVD MPEG II playback has 4x bandwidth requirements which easily overwhelms the traditional 8Mhz ISA type interface. O2Micro addresses this deficiency in the ZV port specification by introducing a 1x, 2x and 4x clock rate control in the O2Micro Control1 Register (D0h) bits 18-19. Enabling the DVD Enhanced ZV port will increases the PC Card clock by a factor of 1x, 2x, and 4x, greatly increasing the available bandwidth for video data.

## 2. PC Card Detect and Power Management

Prior to 1995, only 5V PC Card slots existed until the 1995 PCMCIA PC Card standard introduced the 3.3V CardBus and 3.3V/5V card slots. It is now possible to design CardBus cards and 16-bit PC Cards which use a 3.3V supply for added power savings. Unfortunately, this complicates the hot insertion and card recognition schemes, since it is now possible to damage a 3.3V card by inserting it into a socket pre-configured for 5V. A PC Card socket can no longer maintain default 5V operation configuration. Voltage requirements and card type must now be detected before applying power. The OZ6812 addresses this by implementing a hardware/software interrogation procedure initiated at card insertion.

### 2.1. PC Card Sensing

The OZ6812 supports hot insertion and detection of either CardBus or 16-bit PC Cards. Card insertion detection, determining card type and setting the initial socket Vcc consists of a two step process. The pins CD2, CD1 for 16bit cards, and CCD1# and CCD2# for CardBus cards are utilized to detect card insertion. The pins VS2 and VS1 for 16-bit cards, and CVS2 and CVS1 for CardBus cards are used to determine card type and the required initial socket voltage. It is the PC Card designer's responsibility to connect these four pins in the proper configuration corresponding to the type of card (16 bit or CardBus) and the supply voltage requirements.

Table 1 shows how the OZ6812 would interpret a PC Card's detect and voltage pins for initial socket voltage and card type. The x.x and y.y operating voltages are supported, even though they are not yet defined by the PC Card Specification. The OZ6812 assumes a low-voltage key (CardBus-capable socket in system).

| CD1/ CCD1# | CD2/ CCD2# | VS1/ CVS1 | VS2/CVS2 | Card Type | Initial Vcc    |

|------------|------------|-----------|----------|-----------|----------------|

| ground     | Ground     | open      | Open     | 16-Bit    | 5 vdc          |

| ground     | Ground     | ground    | Open     | 16-Bit    | 3.3 vdc        |

| ground     | Ground     | open      | Ground   | 16-Bit    | x.x vdc        |

| ground     | Ground     | ground    | Ground   | 16-Bit    | 3.3 & x.x vdc  |

| CVS1       | Ground     | CCD1#     | Open     | CardBus   | 3.3 vdc        |

| ground     | CVS2       | open      | CCD2#    | CardBus   | x.x vdc        |

| ground     | CVS1       | CCD2#     | Open     | CardBus   | y.y vdc        |

| ground     | CVS2       | ground    | CCD2#    | CardBus   | 3.3 & x.x      |

| ČVS2       | Ground     | open      | CCD1#    | CardBus   | x.x & y.y      |

| ground     | CVS1       | CCD2#     | Ground   | CardBus   | 3.3, x.x & y.y |

Table 1. Card detect and Voltage Sense

#### 2.2. Socket Power Control

Socket power is automatically disabled on power up reset or when no card is detected in the socket. Software can enable socket power when a card is detected on power up (card detect input pins CD[2:1] asserted low) or from a card insertion management interrupt (generated by sensing a change in state on CD[2:1]). When a card is removed from a socket, the OZ6812 will automatically disable the Vcc and Vpp supplies to the socket and notify the system via management interrupts. The OZ6812 provides control to the required pins over an external parallel or serial socket power-control device to switch socket voltages on or off.

#### Parallel Socket Power Control Mode:

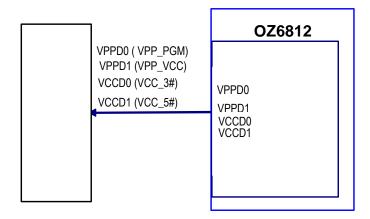

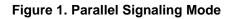

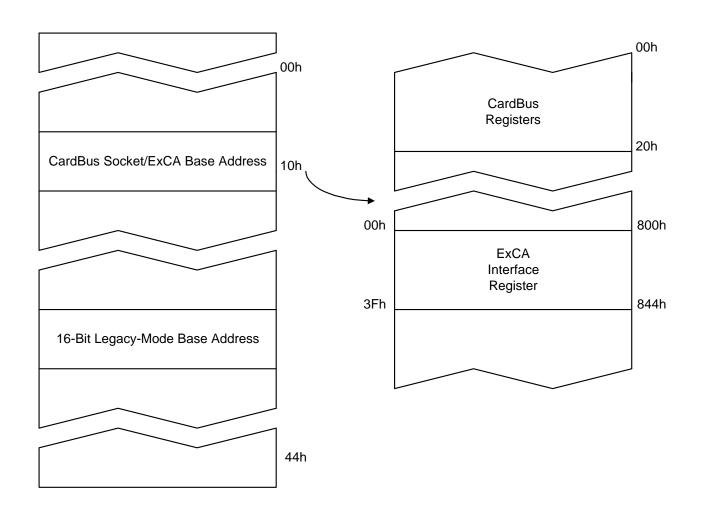

The OZ6812 supports a conventional parallel socket power interface. The OZ6812 generates four pins **VPPD0** (VPP\_PGM), VPPD1 (VPP\_VCC), VCCD0# (VCC\_3#) and **VCCD1#** (VCC\_5#) for each socket to control the socket power through an external power FET chip such as the Micrel MIC2563A. See Figure 1.

#### Serial Signaling Mode:

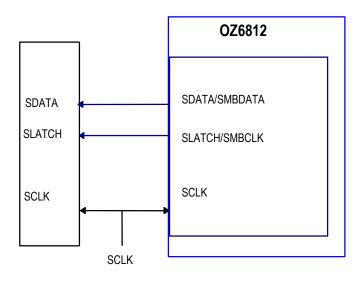

In this mode, power to the socket is controlled by software via the PC Card Socket Register/Control Base Register (PCI Configuration Register 10h). When a legal Vcc or Vpp is requested by PCMCIA software, the OZ6812 uses a synchronous serial protocol to communicate with a PC Card power interface switch. The OZ6812 uses a threewire bus interface: clock (SCLK pin 74), data (SDATA pin 73), and latch line (SLATCH pin 71) to communicate with the power switch. Power information encoded on the serial SDATA line will simultaneously specify Vpp and Vcc settings for the socket. The SCLK, derived from a 32Khz source, serves as a reference clock for the OZ6812 and as a clock to the interface switch. Serial power information is transferred over the SDATA line at SCLK clock rates and synchronously latched in the interface switch by the SLATCH signal. See Figure 2.

# System Management Bus (SMBus) Signaling Mode:

In this mode, the OZ6812 supports the System Management Bus (SMBus) protocol which employs a two wire serial interface; SMBDATA (pin 73) and SMBCLK (pin 74) as a reference for the OZ6812. The Maxim MAX 1601 dualchannel PC Card power switching network supports this SMBus protocol and accepts serial data from the SMBDATA pin and a serial clock from the SMBCLK pin. See Figure 3.

Figure 3. SMBus Signaling Mode

## 3. Interrupt Support

The OZ6812 detects interrupts and/or events at the PC Card interface and notifies the host interrupt controller via one of several interrupt signaling protocols. The OZ6812 supports two classes of interrupts; socket/card functional interrupts initiated by PC Cards activating their RDY/IREQ# signal and CSC management interrupts. CSC management interrupts are events at the PC Card interface which cause notification of host software for service. CSC management interrupts are triggered by PC Card/CardBus status changes such as; Card insertion or removal, Battery dead indicator (BVD1) or I/O-type card status change (STSCHG#); Battery warning indicator (BVD2) change on a memory-type card.

The 16-bit I/O and CardBus PC Cards both have similar methods for signaling interrupts and also use two signals: one to indicate a change in card status, the other dedicated to request interrupt servicing from the host. A 16-bit memory PC Card uses the BVD1 and BVD2 signals to indicate changes in battery conditions on the card and the READY signal to insert wait states during memory card data transfers. Card insertion and removal events are independent of card type since the same card detect signal are used in both cases and the OZ6812 cannot distinguish between card types.