## PC Card Controller compliant with PCMCIA 2.1/JEIDA 4.2

RF5C296/RF5C396L/RB5C396/RF5C396

## **APPLICATION MANUAL**

#### **NOTICE**

- 1. The products and the product specifications described in this application manual are subject to change or discontinuation of production without notice for reasons such as improvement. Therefore, before deciding to use the products, please refer to Ricoh sales representatives for the latest information thereon.

- 2. This application manual may not be copied or otherwise reproduced in whole or in part without prior written consent of Ricoh.

- 3. Please be sure to take any necessary formalities under relevant laws or regulations before exporting or otherwise taking out of your country the products or the technical information described herein.

- 4. The technical information described in this application manual shows typical characteristics of and example application circuits for the products. The release of such information is not to be construed as a warranty of or a grant of license under Ricoh's or any third party's intellectual property rights or any other rights.

- 5. The products listed in this document are intended and designed for use as general electronic components in standard applications (office equipment, computer equipment, measuring instruments, consumer electronic products, amusement equipment etc.). Those customers intending to use a product in an application requiring extreme quality and reliability, for example, in a highly specific application where the failure or misoperation of the product could result in human injury or death (aircraft, spacevehicle, nuclear reactor control system, traffic control system, automotive and transportation equipment, combustion equipment, safety devices, life support system etc.) should first contact us.

- 6. We are making our continuous effort to improve the quality and reliability of our products, but semiconductor products are likely to fail with certain probability. In order prevent any injury to persons or damages to property resulting from such failure, customers should be careful enough to incorporate safety measures in their design, such as redundancy feature, fire-containment feature and fail-safe feature. We do not assume any liability or responsibility for any loss or damage arising from misuse or inappropriate use of the products.

- 7. Anti-radiation design is not implemented in the products described in this application manual.

- 8. Please contact Ricoh sales representatives should you have any questions or comments concerning the products or the technical information.

June 1995

# RF5C296/RF5C396L/RB5C396/RF5C396 APPLICATION MANUAL

## CONTENTS

| OUTLINE ·····                                                         |    |

|-----------------------------------------------------------------------|----|

| FEATURES ·····                                                        |    |

| APPLICATIONS                                                          |    |

| PIN CONFIGURATION (RF5C296) ······                                    |    |

| PIN ASSIGNMENTS (RF5C296) · · · · · · · · · · · · · · · · · · ·       | 4  |

| PIN CONFIGURATION (RF5C396L/RF5C396) ······                           | 5  |

| PIN ASSIGNMENTS (RF5C396L/RF5C396) ······                             | 6  |

| PIN CONFIGURATION (RB5C396) ·······                                   | 8  |

| PIN ASSIGNMENTS (RB5C396) · · · · · · · · · · · · · · · · · · ·       |    |

| PIN DESCRIPTION ······                                                | 11 |

| 1. ISA Bus Interface ·····                                            | 11 |

| 2. Card Slot Interface · · · · · · · · · · · · · · · · · · ·          | 13 |

| 3. Other Control Pins · · · · · · · · · · · · · · · · · · ·           |    |

| 4. Power and Ground Supply Pins · · · · · · · · · · · · · · · · · · · | 16 |

| BLOCK DIAGRAM ······                                                  |    |

| FUNCTIONAL DESCRIPTION                                                | 18 |

| 1. Address Mapping ·····                                              | 18 |

| 2. Power Management ·····                                             |    |

| 3. Mixed Voltage Operation ·····                                      | 19 |

| 4. Address Mapping ·····                                              | 21 |

| 5. Bus Sizing·····                                                    | 21 |

| 6. Internal Register Access ·····                                     | 22 |

| 7. Plural Slots System ·····                                          | 23 |

| 8. PCMCIA-ATA Mode·····                                               | 24 |

| 9. DMA Mode · · · · · · · · · · · · · · · · · · ·                     |    |

| INTERNAL REGISTERS······                                              |    |

| 1.Chip Control ·····                                                  | 27 |

|                                                                       |    |

| 2. I/O Mapping·····                                          |    |

|--------------------------------------------------------------|----|

| 3. Memory Mapping·····                                       |    |

| 4. Expansion Function ·····                                  |    |

| 5. I/O Address Remapping·····                                |    |

| 6. Summary of Internal Register ·····                        |    |

| HARDWARE DESIGN CONSIDERATIONS······                         |    |

| 1. Initial Value Setting Pins ·····                          |    |

| 2. Connections to System Bus ·····                           |    |

| 3. Connections to PCMCIA Slot······                          |    |

| 4. Connections to Power Supply System ·····                  |    |

| 5. Connecting Multiple Units of RF5C296 or RF5C396 ·····     |    |

| SOFTWARE DESIGN CONSIDERATIONS                               |    |

| 1. Confirmation of Access to Internal Registers              |    |

| 2. Identification of PC Card Types ·····                     |    |

| 3. Address Mapping and Address Window Setting ······         | 54 |

| 4. Interrupt Processing ·····                                |    |

| 5. Card Slot Pin Status Indication and Register Setting····· |    |

| ABSOLUTE MAXIMUM RATINGS ······                              |    |

| DC CHARACTERISTICS ······                                    |    |

| AC CHARACTERISTICS······                                     |    |

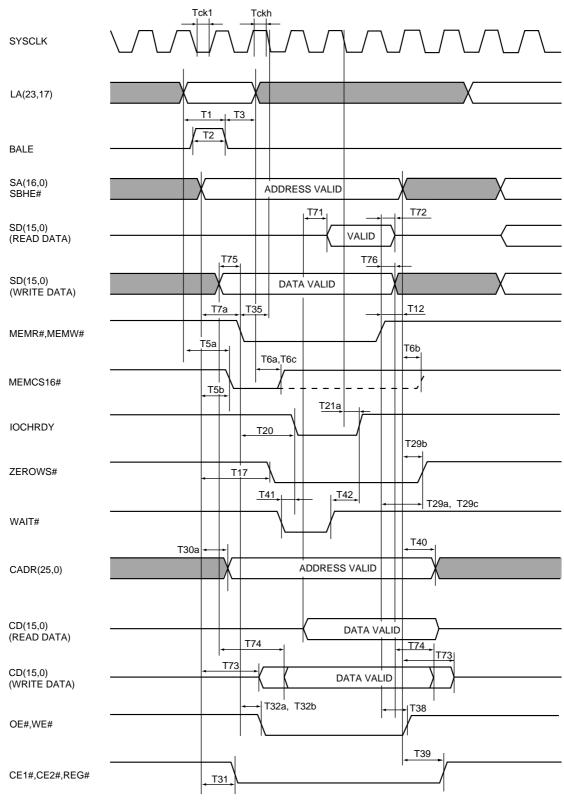

| 1. 8/16bit Memory Cycle ·····                                |    |

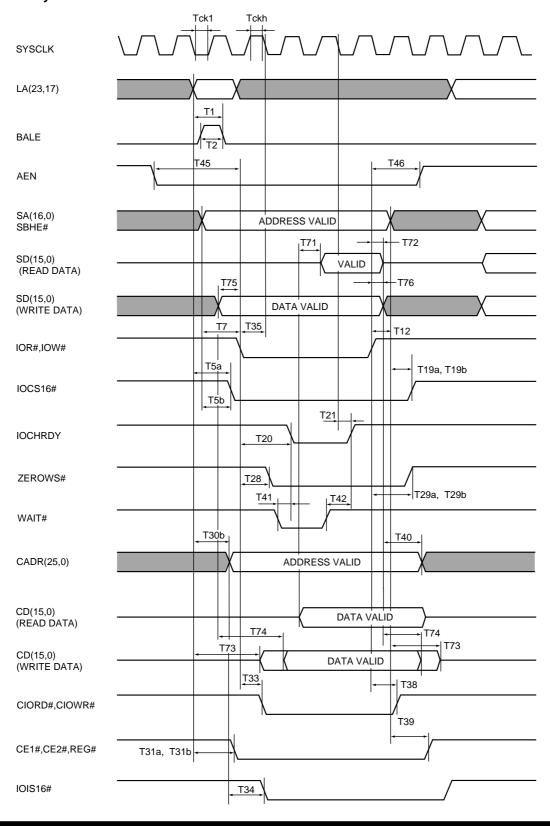

| 2. 8/16bit I/O Cycle ·····                                   |    |

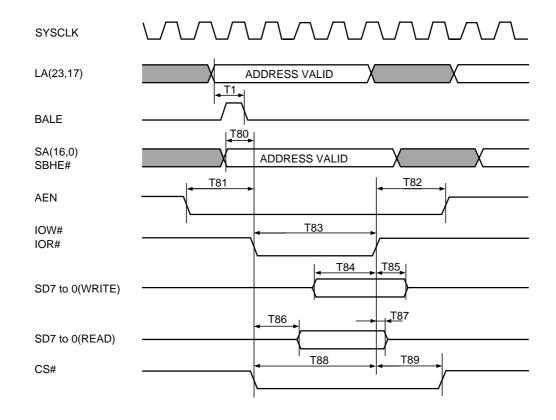

| 3. Internal 8bits Register Access Cycle ······               |    |

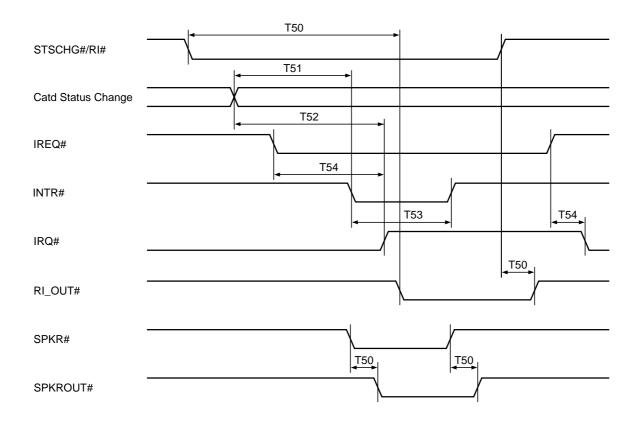

| 4. Interrupt, Ring Indicate Speaker ······                   |    |

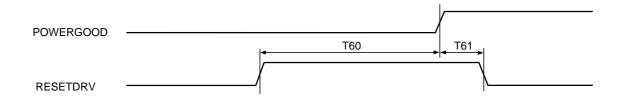

| 5. Reset from POWERGOOD ·····                                |    |

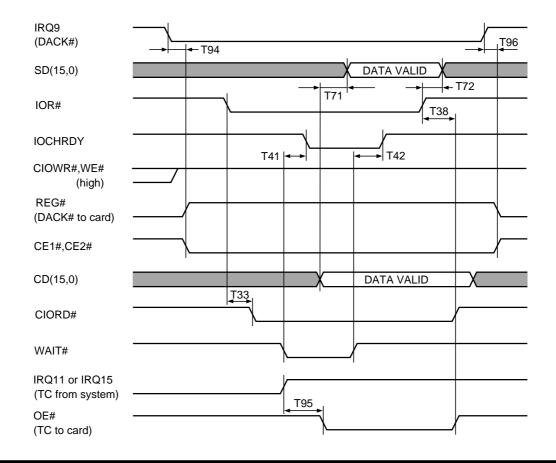

| 6. DMA Read Cycle Timing ·····                               |    |

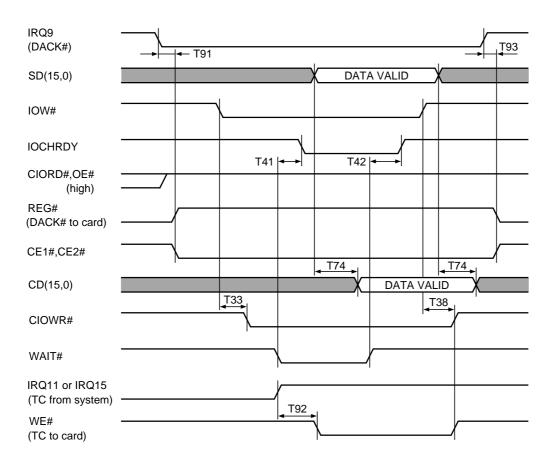

| 7. DMA Write Cycle Timing ·····                              |    |

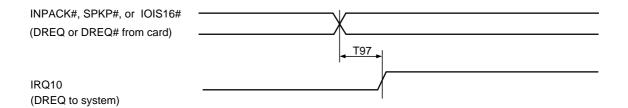

| 8. DMA Request Timing ·····                                  |    |

| BUS SYSTEM·····                                              |    |

| SUPPORT ENVIRONMENT······                                    |    |

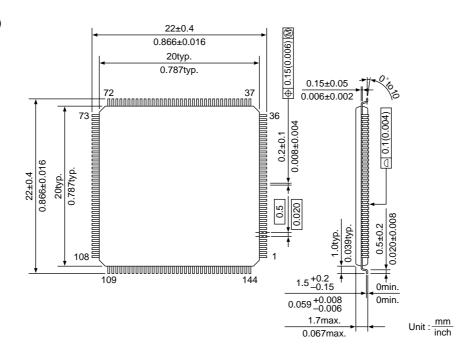

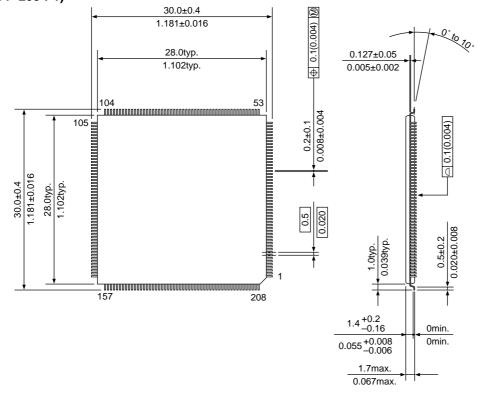

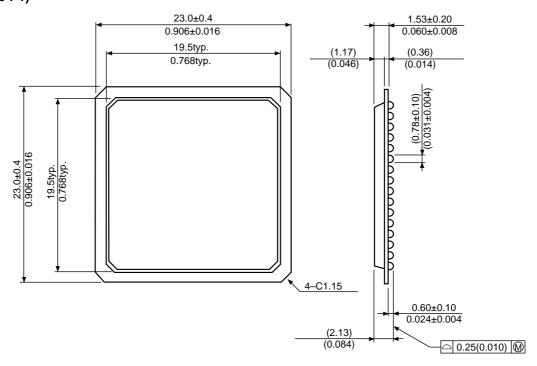

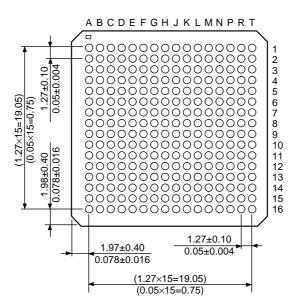

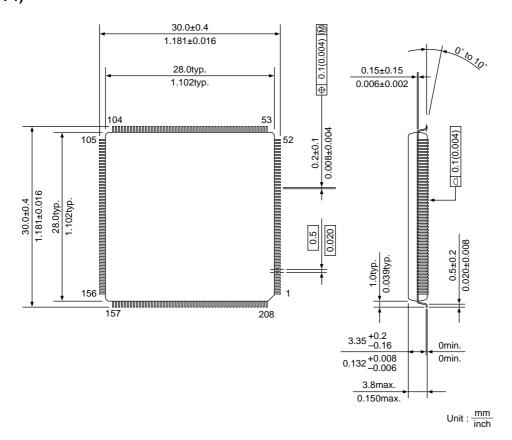

| PACKAGE DIMENSIONS ······                                    | 86 |

|                                                              |    |

## COMPLIANT WITH PCMCA2.1/JEIDA4.2 PC CARD CONTROLLER

## RF5C296/RF5C396L/RB5C396/RF5C396

#### OUTLINE

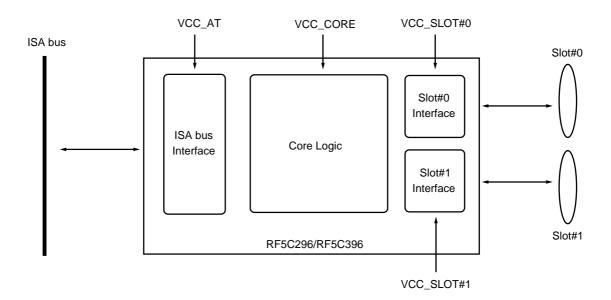

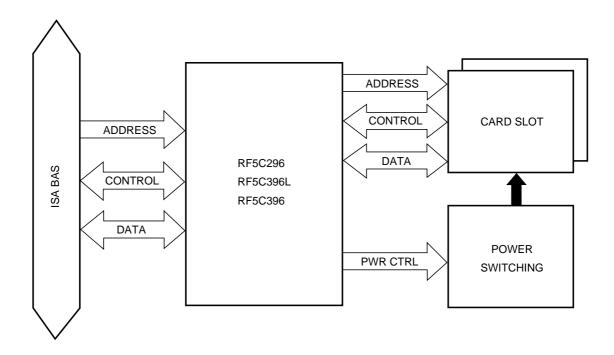

The RF5C296, the RF5C396L, the RB5C396, and the RF5C396 are enhanced version of the RF5C266 and RF5C366, LSIs functioning as controllers for interfacing IC memory cards, modems, and I/O cards, such as HDDs, to system buses in compliance with the PCMCIA2.1 or JEIDA4.2 Standard. These controller LSIs can be used to configure an ISA bus system which supports PC cards.

The RF5C296 supports one PC card slot while the RF5C396L, the RB5C396 and the RF5C396 support two PC card slots. Incorporating a buffer and a transceiver, each of these devices can be directly coupled to the ISA system bus and the PC card slots. The devices are also capable of providing an independent power supply of 3.3V or 5V for each slot interface, system bus, and core logic. Further, they effect substantial space savings through implementation in slimline packages (i.e. the 144pin LQFP for the RF5C296, the 208pin LQFP for the RF5C396L, the 256pin PBGA for the RB5C396 and the 208pin QFP for the RF5C396).

Unless otherwise noted, the RF5C396L, the RB5C396 and the RF5C396 are collectively referred to as the RF5C396 in this manual.

#### **FEATURES**

- Enhanced version of RF5C266/RF5C366

- · DMA mode support

- · Enhanced power management

- · INPACK# pin support

- · Available in thin (t=1.5mm) LQFP and PBGA

- Compliant with PCMCIA2.1/JEIDA4.2

- i82365SL B\_Step compatible register set

- Direct connection to PCMCIA2.1/JEID4.2 PC Card slot

- Easy host interface using ISA I/O addresses 3E0h, 3E1h

- Direct connection to ISA Bus

- · Programmable IRQs to level mode or edge trigger mode

- Enhanced Power Management based on socket and window inactivity

- PCMCIA-AT-A Disk interface support

- 8bit cycles follow SBHE# independent of programmed window size

- 5 programmable memory windows per slot

- 2 programmable I/O windows per slot

- 3.3V & 5V Mixed Voltage Operation

- DMA mode Support

#### • PACKAGES

· RF5C296 144pin LQFP (t=1.7mm)

· RF5C396L 208pin LQFP (t=1.7mm)

· RB5C396 256pin PBGA (23×23)

· RF5C396 208pin QFP

## **APPLICATIONS**

- PC (Notebook Type, Pen-based Type and Palm Top Type)

- Docking Station

- PDA

- Handy Terminal

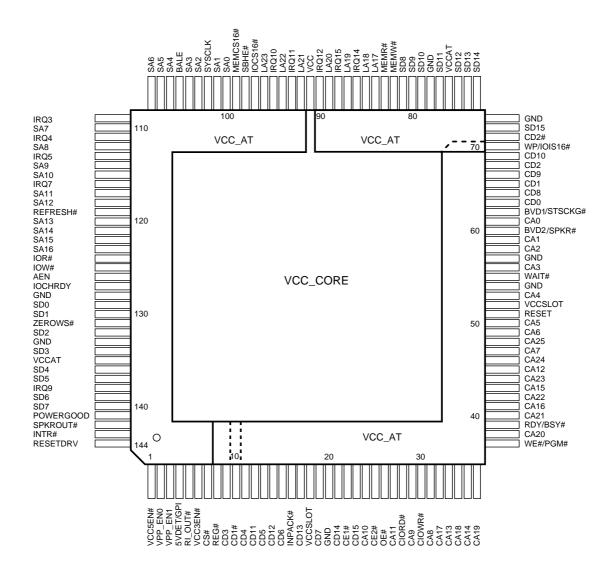

### PIN CONFIGURATION

• RF5C296 Pin Assignments (Top View)

\*) CD1# and CD2# are powered by VCC\_AT

## **PIN ASSIGNMENTS**

#### • RF5C296

| Pin No. | Symbol    | Pin No. | Symbol       | Pin No. | Symbol   | Pin No. | Symbol    |

|---------|-----------|---------|--------------|---------|----------|---------|-----------|

| 1       | VCC5EN#   | 37      | WE#/PGM#     | 73      | SD14     | 109     | IRQ3      |

| 2       | VPP_EN0   | 38      | CA20         | 74      | SD13     | 110     | SA7       |

| 3       | VPP_EN1   | 39      | RDY/BSY#     | 75      | SD12     | 111     | IRQ4      |

| 4       | 5VDET/GPI | 40      | CA21         | 76      | VCCAT    | 112     | SA8       |

| 5       | RIOUT#    | 41      | CA16         | 77      | SD11     | 113     | IRQ5      |

| 6       | VCC3EN#   | 42      | CA22         | 78      | GND      | 114     | SA9       |

| 7       | CS#       | 43      | CA15         | 79      | SA10     | 115     | SA10      |

| 8       | REG#      | 44      | CA23         | 80      | SD9      | 116     | IRQ7      |

| 9       | CD3       | 45      | CA12         | 81      | SD8      | 117     | SA11      |

| 10      | CD1#      | 46      | CA24         | 82      | MEMW#    | 118     | SA12      |

| 11      | CD4       | 47      | CA7          | 83      | MEMR#    | 119     | REFRESH#  |

| 12      | CD11      | 48      | CA25         | 84      | LA17     | 120     | SA13      |

| 13      | CD5       | 49      | CA6          | 85      | LA18     | 121     | SA14      |

| 14      | CD12      | 50      | CA5          | 86      | IRQ14    | 122     | SA15      |

| 15      | CD6       | 51      | RESET        | 87      | LA19     | 123     | SA16      |

| 16      | INPACK#   | 52      | VCCSLOT      | 88      | IRQ15    | 124     | IOR#      |

| 17      | CD13      | 53      | CA4          | 89      | LA20     | 125     | IOW#      |

| 18      | VCCSLOT   | 54      | GND          | 90      | IRQ12    | 126     | AEN       |

| 19      | CD7       | 55      | WAIT#        | 91      | VCC      | 127     | IOCHRDY   |

| 20      | GND       | 56      | CA3          | 92      | LA21     | 128     | GND       |

| 21      | CD14      | 57      | GND          | 93      | IRQ11    | 129     | SD0       |

| 22      | CE1#      | 58      | CA2          | 94      | LA22     | 130     | SD1       |

| 23      | CD15      | 59      | CA1          | 95      | IRQ10    | 131     | ZEROWS#   |

| 24      | CA10      | 60      | BVD2/SPKR#   | 96      | LA23     | 132     | SD2       |

| 25      | CE2#      | 61      | CA0          | 97      | IOCS16#  | 133     | GND       |

| 26      | OE#       | 62      | BVD1/STSCHG# | 98      | SBHE#    | 134     | SD3       |

| 27      | CA11      | 63      | CD0          | 99      | MEMCS16# | 135     | VCCAT     |

| 28      | CIORD#    | 64      | CD8          | 100     | SA0      | 136     | SD4       |

| 29      | CA9       | 65      | CD1          | 101     | SA1      | 137     | SD5       |

| 30      | CIOWR#    | 66      | CD9          | 102     | SYSCLK   | 138     | IRQ9      |

| 31      | CA8       | 67      | CD2          | 103     | SA2      | 139     | SD6       |

| 32      | CA17      | 68      | CD10         | 104     | SA3      | 140     | SD7       |

| 33      | CA13      | 69      | WP/IOIS16#   | 105     | BALE     | 141     | POWERGOOD |

| 34      | CA18      | 70      | CD2#         | 106     | SA4      | 142     | SPKROUT#  |

| 35      | CA14      | 71      | SD15         | 107     | SA5      | 143     | INTR#     |

| 36      | CA19      | 72      | GND          | 108     | SA6      | 144     | RESETDRV  |

<sup>\*)</sup> I : Active "low" signals are indicated by "#".

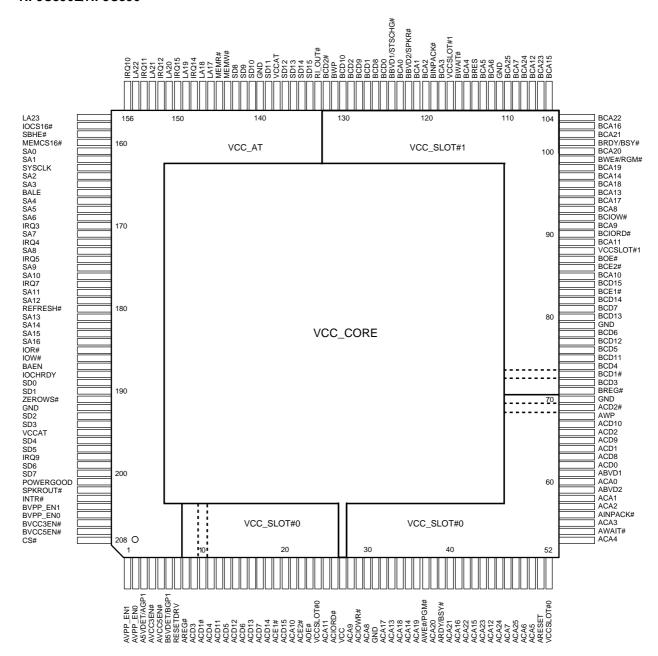

### PIN CONFIGURATION

#### RF5C396L/RF5C396

\*) ACD1# ,ACD2# ,BCD1#,BCD2# are powered by VCC\_AT

## **PIN ASSIGNMENTS**

#### • RF5C396L/RF5C396

| Pin No. | Symbol      | Pin No. | Symbol        | Pin No. | Symbol    | Pin No. | Symbol        |

|---------|-------------|---------|---------------|---------|-----------|---------|---------------|

| 1       | AVPP_EN1    | 37      | AWE#/PGM#     | 73      | BCD1#     | 109     | BCA7          |

| 2       | AVPP_EN0    | 38      | ACA20         | 74      | BCD4      | 110     | BCA25         |

| 3       | A5VDET/AGPI | 39      | ARDY/BSY#     | 75      | BCD11     | 111     | GND           |

| 4       | AVCC3EN#    | 40      | ACA21         | 76      | BCD5      | 112     | BCA6          |

| 5       | AVCC5EN#    | 41      | ACA16         | 77      | BCD12     | 113     | BCA5          |

| 6       | B5VDET/BGPI | 42      | ACA22         | 78      | BCD6      | 114     | BRESET        |

| 7       | RESETDRV    | 43      | ACA15         | 79      | GND       | 115     | BCA4          |

| 8       | AREG#       | 44      | ACA23         | 80      | BCD13     | 116     | BWAIT#        |

| 9       | ACD3        | 45      | ACA12         | 81      | BCD7      | 117     | VCCSLOT#1     |

| 10      | ACD1#       | 46      | ACA24         | 82      | BCD14     | 118     | BCA3          |

| 11      | ACD4        | 47      | ACA7          | 83      | BCE1#     | 119     | BINPACK#      |

| 12      | ACD11       | 48      | ACA25         | 84      | BCD15     | 120     | BCA2          |

| 13      | ACD5        | 49      | ACA6          | 85      | BCA10     | 121     | BCA1          |

| 14      | ACD12       | 50      | ACA5          | 86      | BCE2#     | 122     | BBVD2/SPKR#   |

| 15      | ACD6        | 51      | ARESET        | 87      | BOE#      | 123     | BCA0          |

| 16      | ACD13       | 52      | VCCSLOT#0     | 88      | VCCSLOT#1 | 124     | BBVD1/STSCHG# |

| 17      | ACD7        | 53      | ACA4          | 89      | BCA11     | 125     | BCD0          |

| 18      | ACD14       | 54      | AWAIT#        | 90      | BCIORD#   | 126     | BCD8          |

| 19      | ACE1#       | 55      | ACA3          | 91      | BCA9      | 127     | BCD1          |

| 20      | ACD15       | 56      | AINPACK#      | 92      | BCIOWR#   | 128     | BCD9          |

| 21      | ACA10       | 57      | ACA2          | 93      | BCA8      | 129     | BCD2          |

| 22      | ACE2#       | 58      | ACA1          | 94      | BCA17     | 130     | BCD10         |

| 23      | AOE#        | 59      | ABVD2/SPKR#   | 95      | BCA13     | 131     | BWP/IOIS16#   |

| 24      | VCCSLOT#0   | 60      | ACA0          | 96      | BCA18     | 132     | BCD2#         |

| 25      | ACA11       | 61      | ABVD1/STSCHG# | 97      | BCA14     | 133     | RIOUT#        |

| 26      | ACIORD#     | 62      | ACD0          | 98      | BCA19     | 134     | SD15          |

| 27      | VCC         | 63      | ACD8          | 99      | BWE#/PGM# | 135     | SD14          |

| 28      | ACA9        | 64      | ACD1          | 100     | BCA20     | 136     | SD13          |

| 29      | ACIOWR#     | 65      | ACD9          | 101     | BRDY/BSY# | 137     | SD12          |

| 30      | ACA8        | 66      | ACD2          | 102     | BCA21     | 138     | VCCAT         |

| 31      | GND         | 67      | ACD10         | 103     | BCA16     | 139     | SD11          |

| 32      | ACA17       | 68      | AWP/IOIS16#   | 104     | BCA22     | 140     | GND           |

| 33      | ACA13       | 69      | ACD2#         | 105     | BCA15     | 141     | SD10          |

| 34      | ACA18       | 70      | GND           | 106     | BCA23     | 142     | SD9           |

| 35      | ACA14       | 71      | BREG#         | 107     | BCA12     | 143     | SD8           |

| 36      | ACA19       | 72      | BCD3          | 108     | BCA24     | 144     | MEMW#         |

| Pin No. | Symbol   | Pin No. | Symbol | Pin No. | Symbol   | Pin No. | Symbol    |

|---------|----------|---------|--------|---------|----------|---------|-----------|

| 145     | MEMR#    | 161     | SA0    | 177     | IRQ7     | 193     | SD2       |

| 146     | LA17     | 162     | SA1    | 178     | SA11     | 194     | SD3       |

| 147     | LA18     | 163     | SYSCLK | 179     | SA12     | 195     | VCCAT     |

| 148     | IRQ14    | 164     | SA2    | 180     | REFRESH# | 196     | SD4       |

| 149     | SA19     | 165     | SA3    | 181     | SA13     | 197     | SD5       |

| 150     | IRQ15    | 166     | BALE   | 182     | SA14     | 198     | IRQ9      |

| 151     | LA20     | 167     | SA4    | 183     | SA15     | 199     | SD6       |

| 152     | IRQ12    | 168     | SA5    | 184     | SA16     | 200     | SD7       |

| 153     | LA21     | 169     | SA6    | 185     | IOR#     | 201     | POWERGOOD |

| 154     | IRQ11    | 170     | IRQ3   | 186     | IOW#     | 202     | SPKROUT#  |

| 155     | LA22     | 171     | SA7    | 187     | AEN      | 203     | INTR#     |

| 156     | IRQ10    | 172     | IRQ4   | 188     | IOCHRDY  | 204     | BVPP_EN1  |

| 157     | LA23     | 173     | SA8    | 189     | SD0      | 205     | BVPP_EN0  |

| 158     | IOCS16#  | 174     | IRQ5   | 190     | SD1      | 206     | BVCC3EN#  |

| 159     | SBHE#    | 175     | SA9    | 191     | ZEROWS#  | 207     | BVCC5EN#  |

| 160     | MEMCS16# | 176     | SA10   | 192     | GND      | 208     | CS#       |

<sup>\*)</sup> I : Active "low" signals are indicated by "#".

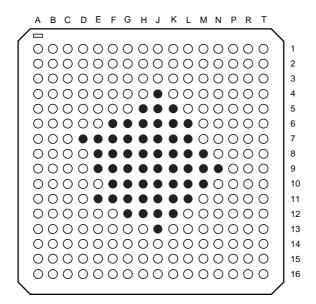

## **PIN CONFIGURATION**

• RB5C396

●:GND

## **PIN ASSIGNMENTS**

#### • RB5C396

| Pin No. | Symbol | Pin No. | Symbol      | Pin No. | Symbol        | Pin No. | Symbol   |

|---------|--------|---------|-------------|---------|---------------|---------|----------|

| A1      | LA22   | B1      | IOCS16#     | C1      | SYSCLK        | D1      | BALE     |

| A2      | LA21   | B2      | IRQ11       | C2      | SA2           | D2      | SA5      |

| A3      | LA19   | В3      | IRQ12       | C3      | SBHE#         | D3      | MEMCS16# |

| A4      | LA17   | B4      | IRQ14       | C4      | IRQ15         | D4      | SA1      |

| A5      | SD8    | B5      | MEMR#       | C5      | LA18          | D5      | IRQ10    |

| A6      | SD11   | В6      | SD9         | C6      | SD10          | D6      | MEMW#    |

| A7      | SD14   | В7      | SD12        | C7      | SD13          | D7      | GND      |

| A8      | BCD2#  | В8      | SD15        | C8      | RIOUT#        | D8      | VCCAT    |

| A9      | BCD9   | В9      | BCD2        | C9      | BWP/IOIS16#   | D9      | BCD10    |

| A10     | BCD0   | B10     | BCD8        | C10     | BCD1          | D10     | BCA0     |

| A11     | BCA1   | B11     | BBVD2/SPKR# | C11     | BBVD1/STSCHG# | D11     | BCA2     |

| A12     | BCA3   | B12     | BINPACK#    | C12     | BWAIT#        | D12     | BCA5     |

| A13     | BRESET | B13     | BCA4        | C13     | BCA24         | D13     | BCA7     |

| A14     | BCA25  | B14     | BCA6        | C14     | BCA12         | D14     | BCA19    |

| A15     | BCA23  | B15     | BCA21       | C15     | BCA20         | D15     | BCA18    |

| A16     | BCA16  | B16     | BRDY/BSY#   | C16     | BCA14         | D16     | BCA17    |

| Pin No. | Symbol    | Pin No. | Symbol    | Pin No. | Symbol  | Pin No. | Symbol        |

|---------|-----------|---------|-----------|---------|---------|---------|---------------|

| E1      | IRQ3      | G1      | IRQ7      | J1      | SA16    | L1      | SD1           |

| E2      | SA7       | G2      | SA11      | J2      | IOW#    | L2      | SD2           |

| E3      | SA6       | G3      | SA12      | J3      | IOR#    | L3      | ZEROWS#       |

| E4      | SA3       | G4      | SA9       | J4      | GND     | L4      | SD4           |

| E5      | LA23      | G5      | SA4       | J5      | GND     | L5      | INTR#         |

| E6      | LA20      | G6      | GND       | J6      | GND     | L6      | GND           |

| E7      | GND       | G7      | GND       | J7      | GND     | L7      | GND           |

| E8      | GND       | G8      | GND       | J8      | GND     | L8      | GND           |

| E9      | GND       | G9      | GND       | J9      | GND     | L9      | GND           |

| E10     | VCCSLOT#1 | G10     | GND       | J10     | GND     | L10     | GND           |

| E11     | GND       | G11     | GND       | J11     | GND     | L11     | GND           |

| E12     | BCA15     | G12     | GND       | J12     | GND     | L12     | ACA2          |

| E13     | BCA22     | G13     | BCIOWR#   | J13     | GND     | L13     | AWP/IOIS16#   |

| E14     | BCA13     | G14     | BCD15     | J14     | BCD6    | L14     | BCD3          |

| E15     | BCA8      | G15     | BCD10     | J15     | BCD12   | L15     | BREG#         |

| E16     | BCIORD#   | G16     | BCE1#     | J16     | BCD5    | L16     | ACD2#         |

| F1      | SA8       | H1      | REFRESH#  | K1      | AEN     | M1      | SD3           |

| F2      | IRQ5      | H2      | SA13      | K2      | SD0     | M2      | SD5           |

| F3      | SA10      | НЗ      | SA15      | К3      | IOCHRDY | M3      | SD6           |

| F4      | IRQ4      | H4      | SA14      | K4      | VCCAT   | M4      | CS#           |

| F5      | SA0       | H5      | GND       | K5      | GND     | M5      | AVPP_EN1      |

| F6      | GND       | H6      | GND       | K6      | GND     | M6      | AVCC5EN#      |

| F7      | GND       | H7      | GND       | K7      | GND     | M7      | ACD4          |

| F8      | GND       | Н8      | GND       | K8      | GND     | M8      | GND           |

| F9      | GND       | H9      | GND       | К9      | GND     | M9      | GND           |

| F10     | GND       | H10     | GND       | K10     | GND     | M10     | GND           |

| F11     | GND       | H11     | GND       | K11     | GND     | M11     | ACA7          |

| F12     | BWE#      | H12     | GND       | K12     | GND     | M12     | ACA4          |

| F13     | BCA9      | H13     | VCCSLOT#1 | K13     | ACD8    | M13     | ABVD1/STSCHG# |

| F14     | BOE#      | H14     | BCD7      | K14     | BCD11   | M14     | ACD9          |

| F15     | BCA11     | H15     | BCD14     | K15     | BCD4    | M15     | ACD10         |

| F16     | BCE2#     | H16     | BCD13     | K16     | BCD1#   | M16     | ACD2          |

| Pin No. | Symbol      | Pin No. | Symbol      | Pin No. | Symbol   | Pin No. | Symbol   |

|---------|-------------|---------|-------------|---------|----------|---------|----------|

| N1      | IRQ9        | P1      | POWERGOOD   | R1      | BVPP_EN0 | T1      | BVCC5EN# |

| N2      | SD7         | P2      | BVPP_EN1    | R2      | BVCC3EN# | T2      | AVPP_EN0 |

| N3      | SPKROUT#    | P3      | A5VDET/AGPI | R3      | AREG#    | Т3      | RESETDRV |

| N4      | B5VDET/BGPI | P4      | AVCC3EN#    | R4      | ACD11    | T4      | ACD1#    |

| N5      | ACD3        | P5      | ACD5        | R5      | ACD6     | Т5      | ACD12    |

| N6      | ACD13       | P6      | ACE1#       | R6      | ACD14    | Т6      | ACD7     |

| N7      | VCCSLOT#0   | P7      | ACE2#       | R7      | ACA10    | Т7      | ACD15    |

| N8      | VCC         | P8      | ACIORD#     | R8      | ACA11    | Т8      | AOE#     |

| N9      | GND         | P9      | ACIOWR#     | R9      | ACA8     | Т9      | ACA9     |

| N10     | ACA21       | P10     | ACA13       | R10     | ACA18    | T10     | ACA17    |

| N11     | ARDY/BSY#   | P11     | ACA19       | R11     | AWE#     | T11     | ACA14    |

| N12     | VCCSLOT#0   | P12     | ACA15       | R12     | ACA16    | T12     | ACA20    |

| N13     | ACA1        | P13     | ACA24       | R13     | ACA23    | T13     | ACA22    |

| N14     | AINPACK#    | P14     | ACA3        | R14     | ACA25    | T14     | ACA12    |

| N15     | ACD1        | P15     | ACA0        | R15     | ACA5     | T15     | ACA6     |

| N16     | ACD0        | P16     | ABVD2/SPKR# | R16     | AWAIT#   | T16     | ARESET   |

## **PIN DESCRIPTION**

#### 1. ISA Bus Interface

| Symbol       | Function                                                                                                                                                                                                                                                                                                                 | Pin                                                                                 | No.                                                                                 | I/O*  | Drive |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------|-------|

| Cymbol       | i unction                                                                                                                                                                                                                                                                                                                | RF5C296                                                                             | RF5C396*1                                                                           | 1/0   | Dilve |

| LA23 to LA17 | ISA Bus System Address 23 to 17                                                                                                                                                                                                                                                                                          | 96,94,92,89,87,85,                                                                  | 157,155,153,151,<br>149,147,146                                                     | I     | _     |

| SA16 to SA0  | ISA Bus System Address 16 to 0                                                                                                                                                                                                                                                                                           | 123,122,121,120,<br>118,117,115,114,<br>112,110,108,107,<br>106,104,103,101,<br>100 | 184,183,182,181,<br>179,178,176,175,<br>173,171,169,168,<br>167,165,164,162,<br>161 | I     | _     |

| AEN          | Address Enable. High signal is input in DMA mode.                                                                                                                                                                                                                                                                        | 126                                                                                 | 187                                                                                 | I     | _     |

| BALE         | Address Latch Enable. This signal latches LA23 pin to LA17 pin.                                                                                                                                                                                                                                                          | 105                                                                                 | 166                                                                                 | I     | _     |

| SBHE#        | System Bus High Byte Enable                                                                                                                                                                                                                                                                                              | 98                                                                                  | 159                                                                                 | I     | _     |

| REFRESH#     | This active low signal indicates that an ISA-bus refresh cycle is either requested or in progress.                                                                                                                                                                                                                       | 119                                                                                 | 180                                                                                 | I     | _     |

| SD15 to SD0  | System Data Bus                                                                                                                                                                                                                                                                                                          | 71,73,74,75,77,79,<br>80,81,140,139,<br>137,136,134,132,<br>130,129                 | 134,135,136,137,<br>139,141,142,143,<br>200,199,197,196,<br>194,193,190,189         | I/O   | 12mA  |

| IOR#         | I/O Port Read                                                                                                                                                                                                                                                                                                            | 124                                                                                 | 185                                                                                 | I     | _     |

| IOW#         | I/O Port Write                                                                                                                                                                                                                                                                                                           | 125                                                                                 | 186                                                                                 | I     | _     |

| MEMR#        | Memory Read                                                                                                                                                                                                                                                                                                              | 83                                                                                  | 145                                                                                 | I     | _     |

| MEMW#        | Memory Write                                                                                                                                                                                                                                                                                                             | 82                                                                                  | 144                                                                                 | I     | _     |

| IOCS16#      | 16bit I/O Transfer Mode Chip Select                                                                                                                                                                                                                                                                                      | 97                                                                                  | 158                                                                                 | O(OD) | 16mA  |

| MEMCS16#     | 16bit Memory Transfer Mode Chip Select                                                                                                                                                                                                                                                                                   | 99                                                                                  | 160                                                                                 | O(OD) | 16mA  |

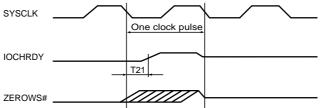

| ZEROWS#      | Zero Wait State                                                                                                                                                                                                                                                                                                          | 131                                                                                 | 191                                                                                 | O(TS) | 12mA  |

| IOCHRDY      | I/O Channel Ready. This active High signal indicates that the accessed device on the ISA-bus is ready to terminate the bus cycle.                                                                                                                                                                                        | 127                                                                                 | 188                                                                                 | O(TS) | 16mA  |

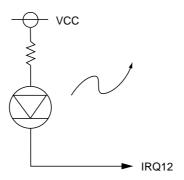

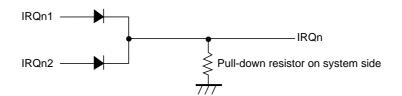

| IRQn         | Interrupt Request Signal. IRQ3, IRQ4, IRQ5, IRQ7, IRQ9, IRQ10, IRQ11, IRQ12, IRQ14, IRQ15. Level mode interrupt or Edge mode interrupt is programmable. IRQ12 can be used as a LED driver. IRQ9, IRQ10, IRQ11, or IRQ15 may be used as system side DACK#, system side DREQ, and system side TC respectively in DMA mode. | 109,111,113,116,<br>138,95,93,90,86,<br>88                                          | 170,172,174,177,<br>198,156,154,152,<br>148,150                                     | O(TS) | 8mA   |

$<sup>\</sup>begin{tabular}{ll} $\star$ ) & I:Input, O:Output, I/O:Input/Output, O(OD):Open Drain Output, O(TS):Tri-State Output. \\ \end{tabular}$

<sup>\*1)</sup> Pin No. of the RB5C396 differ from those of others. Refer to "PIN CONFIGURATION".

| Symbol | Function                                                                                                                    | Pin     | No.       | I/O* | Drive |

|--------|-----------------------------------------------------------------------------------------------------------------------------|---------|-----------|------|-------|

| Symbol | Function                                                                                                                    | RF5C296 | RF5C396*1 | 1/0  | Drive |

| SYSCLK | System Clock Input                                                                                                          | 102     | 163       | I    | _     |

| CS#    | Chip Select input. This signal is use for configuration CS# control power down mode, in case of driving by the I/O address. | 7       | 208       | I    | _     |

<sup>\*)</sup> I: Input, O: Output, I/O: Input/Output, O (OD): Open Drain Output, O (TS): Tri-State Output.

\*1) Pin No. of the RB5C396 differ from those of others. Refer to "PIN CONFIGURATION".

#### 2. Card Slot Interface

| Symbol                    | Function                                                                                                                                                               | Pin                                                                                       | No.                                                                                                                                                                                                                               | I/O*1   | Drive |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|

| Symbol                    | i unction                                                                                                                                                              | RF5C296                                                                                   | RF5C396*2                                                                                                                                                                                                                         | .,,     | Diive |

| CA25 to CA0               | Card Address Output                                                                                                                                                    | 48,46,44,42,40,38,36,<br>34,32,41,43,35,33,45,<br>27,24,29,31,47,49,50,<br>53,56,58,59,61 | Slot#0:<br>48,46,44,42,40,38,36,<br>34,32,41,43,35,33,45,<br>25,21,28,30,47,49,50,<br>53,55,57,58,60<br>Slot#1:<br>110,108,106,104,102,<br>100,98,96,94,103,105,<br>97,95,107,89,85,91,93,<br>109,112,113,115,118,<br>120,121,123 | O(TS)   | 8mA   |

| CD15 to CD8               | Card Data Bus High Byte. Input buffer is disabled when card slot power supply is off or card is not inserted.                                                          | 23,21,17,14,12,68,66,<br>64                                                               | Slot#0:<br>20,18,16,14,12,67,65,63<br>Slot#1:<br>84,82,80,77,75,130,<br>128,126                                                                                                                                                   | I/O(PD) | 8mA   |

| CD7 to CD0                | Card Data Bus Low Byte. Input buffer is disabled when card slot power supply is off or card is not inserted.                                                           | 19,15,13,11,9,67,65,63                                                                    | Slot#0:<br>17,15,13,11,9,66,64,62<br>Slot#1:<br>81,78,76,74,72,129,<br>127,125                                                                                                                                                    | I/O(PD) | 8mA   |

| CE2#                      | Card Enable High Byte                                                                                                                                                  | 25                                                                                        | Slot#0 : 22<br>Slot#1 : 86                                                                                                                                                                                                        | O (TS)  | 8mA   |

| CE1#                      | Card Enable Low Byte                                                                                                                                                   | 22                                                                                        | Slot#0 : 19<br>Slot#1 : 83                                                                                                                                                                                                        | O (TS)  | 8mA   |

| CIORD#                    | Card I/O Read                                                                                                                                                          | 28                                                                                        | Slot#0 : 26<br>Slot#1 : 90                                                                                                                                                                                                        | O (TS)  | 8mA   |

| CIOWR#                    | Card I/O Write                                                                                                                                                         | 30                                                                                        | Slot#0 : 29<br>Slot#1 : 92                                                                                                                                                                                                        | O (TS)  | 8mA   |

| OE#                       | Card Output Enable                                                                                                                                                     | 26                                                                                        | Slot#0 : 23<br>Slot#1 : 87                                                                                                                                                                                                        | O (TS)  | 8mA   |

| WE#/PGM#                  | Card Write Enable/Program                                                                                                                                              | 37                                                                                        | Slot#0 : 37<br>Slot#1 : 99                                                                                                                                                                                                        | O (TS)  | 8mA   |

| BVD1<br>(STSCHG#<br>/RI#) | The battery voltage detect input 1 on the memory PC card, and Card Status Change#/Ring indicate# input on the I/O card.                                                | 62                                                                                        | Slot#0 : 61<br>Slot#1 : 124                                                                                                                                                                                                       | I       | _     |

| BVD2<br>(SPKR#)           | The battery voltage detect input 2 on the memory PC card, and SPEAKER# (Digital Audio) input on the I/O card. This pin may also be used as card side DREQ in DMA mode. | 60                                                                                        | Slot#0 : 59<br>Slot#1 : 122                                                                                                                                                                                                       | I       | _     |

$<sup>\</sup>textbf{*1)} \quad \textbf{I:Input, O:Output, I/O:Input/Output, I/O (PD):Input/Output with Pull-down Register, O (TS):Tri-State Output. } \\$

Pin No. of the RB5C396 differ from those of others. Refer to "PIN CONFIGURATION".

<sup>\*2)</sup> All card slot interface signal names are pretended with A-(slot#0) and B-(slot#1). For example, ACA25 to ACA0 are the card address buses to the slot#0.

| Oh all              | Franction                                                                                                                                                                                                                                                                                                                                                                    | Pin     | No.                             | 1/0*4 | Drive |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------|-------|-------|

| Symbol              | Function                                                                                                                                                                                                                                                                                                                                                                     | RF5C296 | RF5C396*2                       | I/O*1 | Dilve |

| CD1#, CD2#          | Card Detect Input 1 & 2*3                                                                                                                                                                                                                                                                                                                                                    | 10,70   | Slot#0: 10,69<br>Slot#1: 73,132 | I     | _     |

| RDY/BSY#<br>(IREQ#) | READY/BUSY# input on the memory PC card, and IREQ# input on the I/O card.                                                                                                                                                                                                                                                                                                    | 39      | Slot#0:39<br>Slot#1:101         | I     |       |

| REG#                | When this signal is "L" memory access is limited to Attribute memory. During normal access for I/O, this signal must be kept "L". During DMA cycle, this signal must be kept "H".  This pin may also be used as card side DACK in DMA mode.                                                                                                                                  | 8       | Slot#0:8<br>Slot#1:71           | O(TS) | 4mA   |

| WAIT#               | Bus Cycle Wait Input from PC Card                                                                                                                                                                                                                                                                                                                                            | 55      | Slot#0:54<br>Slot#1:116         | I     | _     |

| WP<br>(IOIS16#)     | Write Protect switch input on the memory PC card and, IOIS16# is asserted by PC card when the I/O cycle is 16bit on the I/O. This pin may also be used as card side DREQ in DMA mode.                                                                                                                                                                                        | 69      | Slot#0 : 68<br>Slot#1 : 131     | I     | _     |

| RESET               | Card Reset Output                                                                                                                                                                                                                                                                                                                                                            | 51      | Slot#0:51<br>Slot#1:114         | O(TS) | 4mA   |

| INPACK#             | Input Acknowledge. "L" is output to INPACK# on the PCMCIA bus only when I/O ports accessed during I/O signal read are enabled on PC cards that support this signal.  When INPACK# signal is enabled for RF5C296/RF5C396, I/O signal read data will be output to the system only when the INPACK# signal is enabled. This pin may also be used as card side DREQ in DMA mode. | 16      | Slot#0:56<br>Slot#1:119         | I     | _     |

$<sup>\</sup>textbf{*1)} \quad \textbf{I}: Input, \ \ \textbf{O}: Output, \ \ \textbf{I/O}: Input/Output, \ \ \textbf{O} \ (TS): Tri-State \ Output.$

<sup>\*2)</sup> All card slot interface signal names are pretended with A-(slot#0) and B-(slot#1). For example, ACA25 to ACA0 are the card address buses to the slot #0. Pin No. of the RB5C396 differ from those of others. Refer to "PIN CONFIGURATION".

<sup>\*3)</sup> CD1# and CD2# are powered by VCC\_AT instead of VCC\_SLOT because hot plug-in/out is supported during card slot power is off.

#### 3. Other Control Pins

| Sumbol    | Function                                                                                                                                                                                                                                          | Pi      | I/O*1                      | Dulina   |       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------|----------|-------|

| Symbol    | Function                                                                                                                                                                                                                                          | RF5C296 | RF5C396*2                  | 1/0*1    | Drive |

| POWERGOOD | POWERGOOD input. Connect to GND if not used.                                                                                                                                                                                                      | 141     | 201                        | I        | _     |

| RESETDRV  | Reset Drive Input. This active High signal indicates Main System Cold Reset.                                                                                                                                                                      | 144     | 7                          | I (PD)   | _     |

| SPKROUT#  | Speaker Output. Passes through SPKR# from an I/O card.                                                                                                                                                                                            | 142     | 202                        | O (TS)*3 | 4mA   |

| RI_OUT#   | Ring Indicate Output. Passes through RI_OUT# from an I/O card.                                                                                                                                                                                    | 5       | 133                        | O (TS)*3 | 4mA   |

| INTR#     | Interrupt Request Output                                                                                                                                                                                                                          | 143     | 203                        | O (TS)*3 | 4mA   |

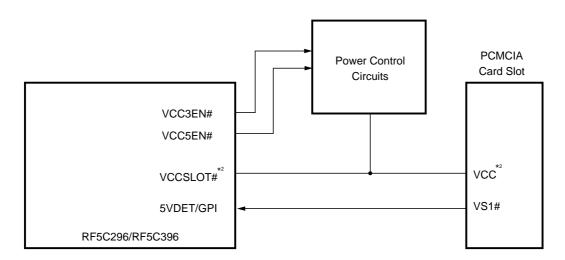

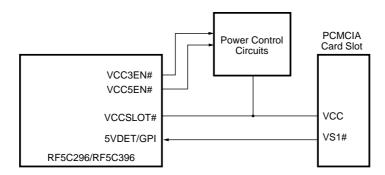

| 5VDET/GPI | 5V detect input/General Purpose Input, on GPI enable. IRQ generation is programmable when transition occurs.  Basically user can use this input arbitrarily. This pin shall be connected to the VSI# in the card slot for use as 5V Detect Input. | 4       | Slot#0:3<br>Slot#1:6       | I (PU)   | _     |

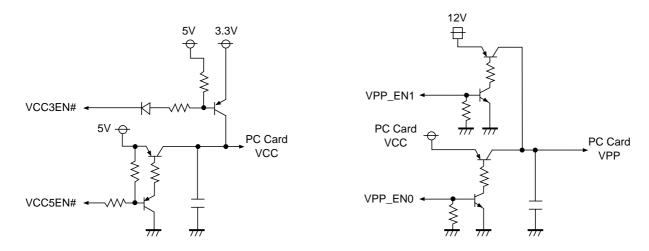

| VCC5EN#   | Power Control (5V)                                                                                                                                                                                                                                | 1       | Slot#0:5<br>Slot#1:207     | О        | 4mA   |

| VCC3EN#   | Power Control (3.3V)                                                                                                                                                                                                                              | 6       | Slot#0 : 4<br>Slot#1 : 206 | О        | 4mA   |

| VPP_EN0   | Program Power Supply Control 0 (VPP_VCC)                                                                                                                                                                                                          | 2       | Slot#0 : 2<br>Slot#1 : 205 | О        | 4mA   |

| VPP_EN1   | Program Power Supply Control 1 (VPP_PGM)                                                                                                                                                                                                          | 3       | Slot#0 : 1<br>Slot#1 : 204 | О        | 4mA   |

<sup>\*1)</sup> I: Input, O: Output, I/O: Input/Output, I (PU): Input with Pull-up Register, I (PD): Input with Pull-down Register, O (TS): Tri-State Output.

<sup>\*2)</sup> All card slot interface signal names are pretended with A-(slot#0) and B-(slot#1). For example, ACA25 to ACA0 are the card address buses to the slot #0.

Pin No. of the RB5C396 differ from those of others. Refer to "PIN CONFIGURATION".

<sup>\*3)</sup> Applicable to only RF5C296.

## 4. Power and Ground Supply Pins

| Symbol  | Function                       | Pin No.                    |                                   |  |  |

|---------|--------------------------------|----------------------------|-----------------------------------|--|--|

| Symbol  | i unction                      | RF5C296                    | RF5C396*1                         |  |  |

| VCC     | VCC for Core Logic             | 91                         | 27                                |  |  |

| VCCAT   | VCC for ISA Interface Signals  | 76, 135                    | 138, 195                          |  |  |

| VCCSLOT | VCC for Card Interface Signals | 18, 52                     | Slot#0 : 24,52<br>Slot#1 : 88,117 |  |  |

| GND     | Ground Pin                     | 20,54,57,72,78,<br>128,133 | 31,70,79,111,140,<br>192          |  |  |

<sup>\*1)</sup> All card slot interface signal names are pretended with A-(slot#0) and B-(slot#1). For example, ACA25 to ACA0 are the card address buses to the slot#0. Pin No. of the RB5C396 differ from those of others. Refer to "PIN CONFIGURATION".

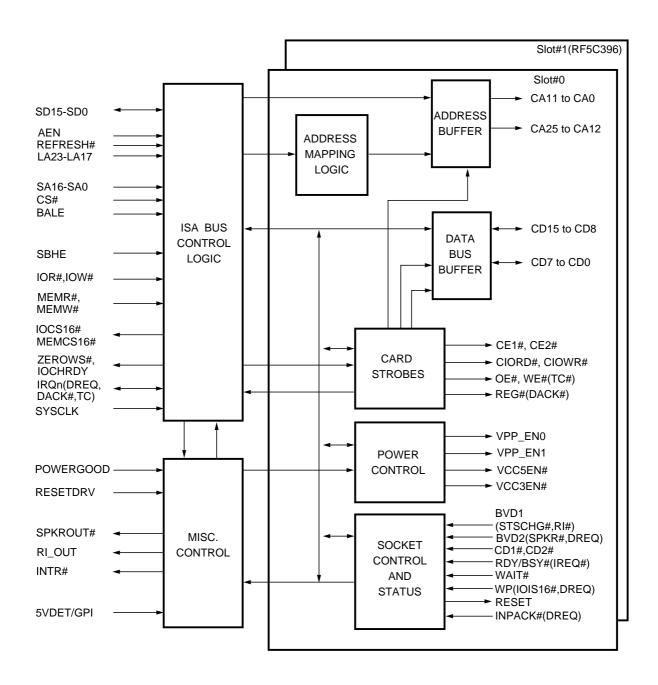

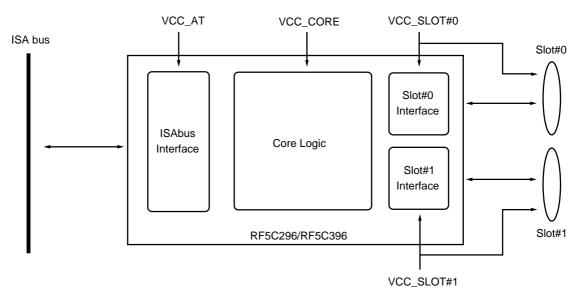

## **BLOCK DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

RF5C296 (RF5C396) is a controller for supporting one (two) card slot compliant to PCMCIA2.1/JEIDA4.2 68pin standard. Direct connection to the card slot is allowed due to the complete buffering of signals to the card. RF5C296/RF5C396 can also interface directly to the ISA bus.

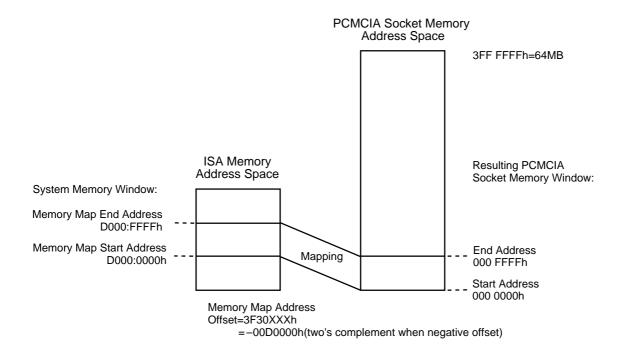

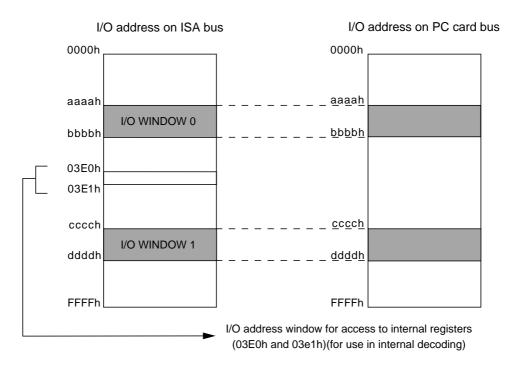

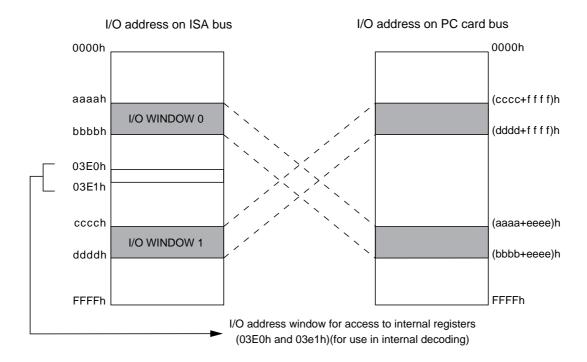

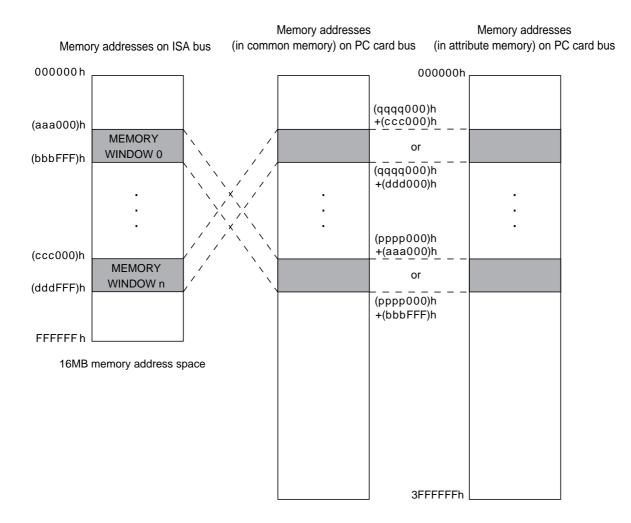

#### 1. Address Mapping

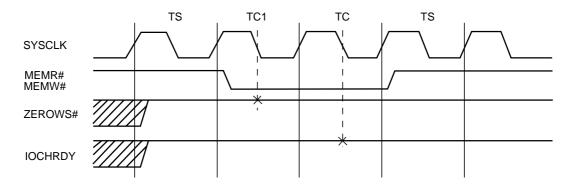

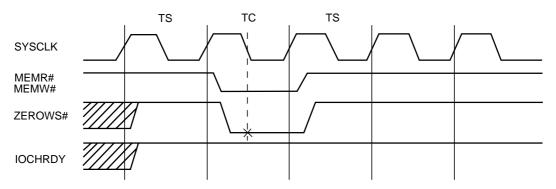

Each socket has five independently enabled and controlled system memory address mapping windows and two independently enabled and controlled system I/O address mapping windows.

Some portions of 64MB common memory and 64MB attribute memory spaces on the PC Cards can be mapped into the smaller 16MB ISA address space.

Mapping of each system memory window can start and stop on any 4kB boundary of ISA system memory above 64kB except for I/O address space of 0000h to 0FFFFh by setting the system memory mapping start register, system memory mapping stop register, and card memory offset register. The summation result (in 2's complement) of the value in the card memory offset register and ISA system address value will result in the memory card address.

Each window has independent control of data bus size, the number of wait cycles, and the selection of common memory area or attribute memory area.

Each I/O window can be mapped with 1byte resolution between 0000h to 0FFFFh in the ISA system address space by setting the I/O start address register and the I/O stop address register. I/O mapping is not allowed during the DMA cycle.

#### 2. Power Management

When card slot is empty or the power supply is off, each card slot has independently power management because each slot has its own buffers and transceivers. In order to achieve the low power consumption especially for the notebook PCs, each address mapping circuit will be powered down when it is not activated. In addition to the function, setting the power down bit in the global control register to "1" enables the RF5C296/RF5C396 to go into the power down mode. There is a single power down control bit which can be written with either a Slot#0 or Slot#1 Global Control Register Index. Setting this bit to "1" goes into the power down mode. Even in the power down mode, RF5C296/RF5C396 can generate a card status change interrupt and PC Card interrupt for I/O cards. The RF5C296/RF5C396 can also generate the RI\_OUT# signal when configured for ring indicate resume from I/O cards. In this Power down mode, the following ISA bus signals will be ignored.

SD[15:0], LA[23:17], SA[16:0], IORD#, IOWR#, AEN, BALE, SYSCLK, MEMW#, MEMR#, SBHE#

#### 3. Mixed Voltage Operation

There are three/four different power nets; VCC for ISA bus interface, VCC for core logic, VCC for card slot interface; to be handled in RF5C296/RF5C396. Each of these power nets can be independently running at 3.3V or 5V. All of the voltage combinations listed on the next page are supported. RF5C296/RF5C396 can operate even with the single power supply of 5V or 3.3V

| Core<br>(VCC_CORE) | Card Slot#0<br>(VCC_SLOT#0) | Card Slot#1<br>(VCC_SLOT#1) | ISA bus Interface<br>(VCC_AT) |

|--------------------|-----------------------------|-----------------------------|-------------------------------|

| 5V                 | 5V                          | 5V                          | 5V                            |

| 3.3V               | 5V                          | 5V                          | 5V                            |

| 3.3V               | 3.3V                        | 5V                          | 5V                            |

| 3.3V               | 5V                          | 3.3V                        | 5V                            |

| 3.3V               | 3.3V                        | 3.3V                        | 5V                            |

| 3.3V               | 5V                          | 5V                          | 3.3V                          |

| 3.3V               | 5V                          | 3.3V                        | 3.3V                          |

| 3.3V               | 3.3V                        | 5V                          | 3.3V                          |

| 3.3V               | 3.3V                        | 3.3V                        | 3.3V                          |

#### Mixed Voltage Operation

When 5VDET/GPI pin is connected to PCMCIA card slot pin #43 (VS1#) as shown in the figure, the following should be considered.

- (1) Interface Status Register bit7\*1 indicate inverted 5VDET/GPI.

- (2) Card Detect and Control Register bit2\*1 (GPI enable) must be kept "0".

- \*1) Refer to page 27 "INTERNAL RESISTERS"

- \*2) As shown in the above table, the RF5C296 and the RF5C396 allow sharing of a power supply between their VCC\_SLOTs and the PCcard slots, provided that the VCC\_CORE should be set to 3.3V.

#### 4. Address Mapping

To prevent any conflict between interrupt request signals derived from the RF5C296 or the RF5C396 and from any other device, the PC card status change, such as fluctuations in the voltage of the battery for the PC card and insertion or removal of the PC card into or from the PC card slot, as well as interrupt request signals (IREQ#) derived from the I/O cards can be assigned to one of the ten interrupt lines for ten interrupt request signals (IRQ15, IRQ14, IRQ12, IRQ11, IRQ10, IRQ9, IRQ7, IRQ5, IRQ4, and IRQ3).

These interrupt requests are programmable to the level mode or the edge trigger mode.

In addition to steering IRQn output, INTR# output is also used as an interrupt output. The INTR# pin signal is normally input to the EXTSMI# pin of the Intel 386SL to output a low-level pulse having three times the width of the SYSCLK pulse at the time of interrupt request generation and a high-level pulse at any other time.

In addition to these interrupts sources, it is programmable that IRQs will be generated when the transition occurs on GPI (General Purpose Input).

If card status change while other card status change interrupt request, second interrupt request pulse is not generated. In this case, the appropriate bit must be set to "1" in the Card Status Change Register (Index : 04h) in the Explicit Write Back Acknowledge Mode to enable interrupt request recognition by the host system interrupt processing routine. Upon interrupt request recognition, the bit is reset to "0".

Incidentally, all the bits in the Card Status Change Register (Index: 04h) are reset to "0" when it is read in any other mode than the Explicit Write Back Acknowledge Mode.

IRQ9, IRQ10, IRQ12, IRQ11 (or IRQ15) are multi-function pins. In PCMCIA-ATA mode, IRQ12 can drive LED. In DMA mode, IRQ9, IRQ10, IRQ11 (or IRQ15) work as DACK#, DREQ, TC.

#### 5. Bus Sizing

In addition to 16bit bus cycle, RF5C296/RF5C396 supports 8bit bus cycle. The 8bit bus cycle to a PC Card can be generated even when the window is configured for 16bit. This means that the combination of SBHE# input and SA0 input override the data size configuration. On 8bit host systems, the SBHE# input must be pulled high (inactive) for proper operation. The following is a truth table of the card enable logic.

| 16bit Window | SBHE# | A0 | CE2# | CE1# |

|--------------|-------|----|------|------|

| YES          | L     | L  | L    | L    |

| YES          | L     | Н  | L    | Н    |

| YES          | Н     | L  | Н    | L    |

| YES          | Н     | Н  | Н    | L    |

| NO           | L     | L  | Н    | L    |

| NO           | L     | Н  | Н    | L    |

| NO           | Н     | L  | Н    | L    |

| NO           | Н     | Н  | Н    | L    |

#### 6. Internal Register Access

All of the control registers of the RF5C296/RF5C396 are 8bit width registers and can be accessed using an indirect indexing scheme. Only two I/O addresses such as (3E1h) and (3E0h) are used to access all control registers.

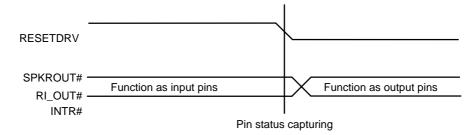

RF5C296/RF5C396 has the external decode mode. In this mode, I/O address is decoded outside and input to CS#. When RESETDRV falls, if the level of INTR# pin is "H" ("L"), internal decode mode (external decode mode) can be selected.

Consequently, these operations can be enabled by externally pulling up or down the INTR# pin to such a degree as not to affect normal operation.

In the Internal Decode Mode, too, the CS# pin should be caused to transition to low level at the time of internal register access (the CS# pin should be caused to transition to high level only in the Power Down Mode).

The Index Register has the bit settings shown below:

| Index Register (3E0h)       |                                         |                |  |  |  |  |  |  |  |

|-----------------------------|-----------------------------------------|----------------|--|--|--|--|--|--|--|

| bit7                        | bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 |                |  |  |  |  |  |  |  |

| "0": Device#0 "1": Device#1 | "0": Slot#0<br>"1": Slot#1              | Register Index |  |  |  |  |  |  |  |

There are 56 control registers provided for each PC card slot. The Index Register has bit7 for indicating a device number depending on the status of the SPKROUT# pin for the RF5C396 or the RI\_OUT# pin for the RF5C296 at the falling edge of the RESETDRV pin signal. For the RF5C296, in particular, the Index Register has bit6 (Slot bit) for indicating a device number depending on the status of the SPKROUT# pin at the falling edge of the RESETDRV pin signal.

Both the SPKROUT# and RI\_OUT# pins operate in the same manner as the INTR# pin described above.

The status of the SPKROUT# pin (for the RF5C396) or the RI\_OUT# pin (for the RF5C296) corresponds to the index range as shown in the tables in "7. Plural (Three) Slot Systems" on the next page. Note that these pins also require their status control for connecting a single unit of the RF5C296 or the RF5C396.

#### 7. Plural Slots System

#### 7.1 Up to 4 slots

As described before, the settings of bit7 and bit6 (Slot bit) in the Index Register depend on the status of the SPKROUT# pin for the RF5C396 or the RI\_OUT# pin for the RF5C296 and on the status of the the SPKROUT# pin for the RF5C296, respectively, at the falling edge of the RESETDRV pin signal. Therefore, 4 slots system can be constructed using plural RF5C296/RF5C396's without modifying I/O address (3E0h, 3E1h)

1-slot system: one RF5C296

2-slot system: one RF5C396 or two RF5C296

3-slot system: one RF5C396 and one RF5C296, or three RF5C296

4-slot system: two RF5C396, or one RF5C396 and two RF5C296, or four RF5C296

The following tables show the relation between the index range and the status of SPKROUT# and RI-OUT# when RESETDRV falls.

#### • RF5C296

| RI_OUT# | SPKROUT# | Device bit | Slot bit | Index Range |

|---------|----------|------------|----------|-------------|

| VDD     | VDD      | 0          | 0        | 00 to 3Fh   |

| VDD     | GND      | 0          | 1        | 40 to 7Fh   |

| GND     | VDD      | 1          | 0        | 80 to BFh   |

| GND     | GND      | 1          | 1        | C0 to EFh   |

#### • RF5C396

| SPKROUT# | Device bit | Slot bit | Index Range |  |

|----------|------------|----------|-------------|--|

| VDD      | 0          | 0        | 00 to 3Fh   |  |

| VDD      | 0          | 1        | 40 to 7Fh   |  |

| GND      | 1          | 0        | 80 to BFh   |  |

| GND      | 1          | 1        | C0 to EFh   |  |

#### Notice

Access to any other index range than is specified at power-on is invalidated while any attempt to read the Index Register results in a data bus output of high impedance.

#### 7.2 Five or More Slots

More than five PC card slots can also be supported through external decoding of the A15 to A1 pin signals for input to the CS# pin and thereby setting of any given I/O addresses of the internal registers for the RF5C296 and the RF5C396.

#### 8. PCMCIA-ATA Mode

$RF5C296/RF5C396 \ supports \ a \ PCMCIA-ATA \ interface \ mode. \ The \ following \ table \ shows \ the \ card \ interface \ signals \ when \ PCMCIA-ATA \ mode \ is \ configured.$

| PIN No. | PCMCIA I/O<br>Interface Signal | ATA Interface Signal | PIN No. | PCMCIA I/O<br>Interface Signal | ATA Interface Signal |  |

|---------|--------------------------------|----------------------|---------|--------------------------------|----------------------|--|

| 1       | GND                            | GND                  | 35      | GND                            | GND                  |  |

| 2       | CD3                            | CD3                  | 36      | CD1#                           | CD1#                 |  |

| 3       | CD4                            | CD4                  | 37      | CD11                           | CD11                 |  |

| 4       | CD5                            | CD5                  | 38      | CD12                           | CD12                 |  |

| 5       | CD6                            | CD6                  | 39      | CD13                           | CD13                 |  |

| 6       | CD7                            | CD7                  | 40      | CD14                           | CD14                 |  |

| 7       | CE1#                           | CE1#                 | 41      | CD15                           | CD15                 |  |

| 8       | CA10                           | CA10                 | 42      | CE2#                           | CE2#                 |  |

| 9       | OE#                            | OE#                  | 43      | NC                             | NC                   |  |

| 10      | CA11                           | CA11                 | 44      | CIORD#                         | CIORD#               |  |

| 11      | CA9                            | CA9                  | 45      | CIOWR#                         | CIOWR#               |  |

| 12      | CA8                            | CA8                  | 46      | CA17                           | CA17                 |  |

| 13      | CA13                           | CA13                 | 47      | CA18                           | CA18                 |  |

| 14      | CA14                           | CA14                 | 48      | CA19                           | CA19                 |  |

| 15      | WE#                            | WE#                  | 49      | CA20                           | CA20                 |  |

| 16      | IREQ#                          | IREQ#(IREQ)          | 50      | CA21                           | *                    |  |

| 17      | VCC                            | VCC                  | 51      | VCC                            | VCC                  |  |

| 18      | VPP1                           | VPP1                 | 52      | VPP2                           | VPP2                 |  |

| 19      | CA16                           | CA16                 | 53      | CA22                           | *                    |  |

| 20      | CA15                           | CA15                 | 54      | CA23                           | *                    |  |

| 21      | CA12                           | CA12                 | 55      | CA24                           | *                    |  |

| 22      | CA7                            | CA7                  | 56      | CA25                           | *                    |  |

| 23      | CA6                            | CA6                  | 57      | RFU                            | NC                   |  |

| 24      | CA5                            | CA5                  | 58      | RESET                          | RESET                |  |

| 25      | CA4                            | CA4                  | 59      | WAIT#                          | WAIT#                |  |

| 26      | CA3                            | CA3                  | 60      | NC                             | NC                   |  |

| 27      | CA2                            | CA2                  | 61      | REG#                           | REG#                 |  |

| 28      | CA1                            | CA1                  | 62      | SPKR#                          | LED#                 |  |

| 29      | CA0                            | CA0                  | 63      | STSCHG#                        | STSCHG#              |  |

| 30      | CD0                            | CD0                  | 64      | CD8                            | CD8                  |  |

| 31      | CD1                            | CD1                  | 65      | CD9                            | CD9                  |  |

| 32      | CD2                            | CD2                  | 66      | CD10                           | CD10                 |  |

| 33      | IOIS16#                        | IOIS16#              | 67      | CD2#                           | CD2#                 |  |

| 34      | GND                            | GND                  | 68      | GND                            | GND                  |  |

<sup>★)</sup> The signals are settable in the internal registers of RF5C296/RF5C396.

Setting the bit0 of the Mode Control Register 1 (Index=1Fh) to "1" configures the corresponding card slot to the PCMCIA-ATA mode. In PCMCIA-ATA mode, if the bit1 of the Mode Control Register is set to "1", the SPKR# input works as an LED input and IRQ12 works as an open drain LED output. At this time SPKROUT# will become inactive.

Bits2 to 6 can be set to specify the values of the CA21 to CA25 pin signals (marked with "\*" in the pin definition table in the PCMCIA-ATA Mode on the previous page). In the PCMCIA-ATA Mode, the output CA21 to CA25 pin signals assume the values thus specified by bits2 to 6.

Bit7 can be set to prevent any conflict between the system floppy disk signal and the card interface signals. When set to "1", bit7 is disabled during reading from an I/O address of 3F7h and 377h on the system data bus.

|                                         | Mode Control Register 1 (Index=1Fh) |     |     |     |     |            |                     |  |  |

|-----------------------------------------|-------------------------------------|-----|-----|-----|-----|------------|---------------------|--|--|

| bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 |                                     |     |     |     |     |            |                     |  |  |

| 377h, 3F7h Disable<br>(in I/O Read)     | A25                                 | A24 | A23 | A22 | A21 | LED Enable | PCMCIA-<br>ATA Mode |  |  |

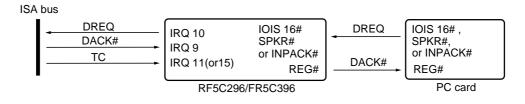

#### 9. DMA Mode

RF5C296/RF5C396 provide the DMA Mode for supporting interfacing with external floppy disk units or other DMA devices via the PC card slots. Setting bit1 of Mode Control Register 3 to "1" enables DMA mode. The DMA data will be transferred to/from DMA capable PC Card with the ISA bus as a DMA master.

On the DMA mode, some of RF5C296/RF5C396 signal pins will be redefined. IRQ9 will work as DACK# input, IRQ10 will work as DREQ output, IRQ11 (or IRQ15) will work as TC input.

DREQ from the PC Card can be assigned to one of three PCMCIA inputs (IOIS16#, SPKR# or INPACK#) by setting bit7 and bit6 of Mode Control Register 2.

DMA transfer between the ISA system memory and the I/O card is available in the following two types:

DMA made configuration

- 1) DMA transfer between the ISA system memory and the I/O card

- 2) DMA transfer between memory in the I/O card and the I/O port via the system data bus.

Notice

Only one slot at a time should be enabled for DMA transfer. And DMA transfer to/from DMA capable PC Card may be 8 or 16bit as shown in the bus sizing table of page 21.

The TC# (terminal count) pin signal input to the PC card becomes active low for output from the OE# pin at a cycle for reading from the PC card (a cycle for writing to the memory) and from the E# pin at a cycle for writing to the PC card (a cycle for reading from the memory). Further, the output REG# pin signal is always held at high level during DMA transfer. Thus, it is easy to distinguish between DMA transfer and ordinary bus cycles. Namely, the REG# pin signal functions as DMA transfer acknowledgment for the PC card.

#### Notice on the DMA mode

- 1) IRQ9, IRQ10 and IRQ11 (or IRQ15) are redefined as DMA signals for ISA Bus. Therefore these signals can not be used as interrupt lines.

- 2) Bit5 of General Control Register must be set to "1" to select I/O card.

- 3) If WP/IOIS16# is used as DREQ, bit4 of Interface Status Register indicates DREQ from PC Card.

- 4) If BVD2/SPKR# is used as DREQ, SPKROUT# and LED output can not be used.

- 5) If INPACK# is used as DREQ, bit2 of Mode Control Register 2 must be kept "0".

- 6) TC input can be assigned to one of two IRQ signals (IRQ11 or IRQ15) by setting bit4 of Mode Control Register .

#### INTERNAL REGISTERS

$RF5C396 \ has the \ registers \ both \ for \ Slot\#0 \ (2) \ and \ Slot\#1 \ (3). \ RF5C296 \ has the \ registers \ only \ for \ Slot\#0 \ (1, \, 2, \, 3).$

The internal registers have default bit settings (immediately after the falling edge of the RESETDRV pin signal when the POWERGOOD pin signal is set to "0") as enumerated below:

#### 1. Chip Control

#### 1.1 Identification and Revision Register\*

Index: 00h Default value: 1000 0011b Read only

bit 7 to bit 6: These bits indicate the type of PC Cards supported by the RF5C296/RF5C396.

| bit7 bit6 |   | Interface    |

|-----------|---|--------------|

| 0         | 0 | I/O Only     |

| 0         | 1 | Memory Only  |

| 1         | 0 | Memory & I/O |

| 1         | 1 | Reserved     |

bit5: Reserved bit4: Reserved bit3: Revision#: 0 bit2: Revision#: 0 bit1: Revision#: 1 bit0: Revision#: 1

#### 1.2 Interface Status Register

Index: 01h Default value: Depends on PC card slot status Read only

bit7 : Indicates the state of the reverse of the GPI pin.